Serviço Público Federal

Ministério da Educação

**Fundação Universidade Federal de Mato Grosso do Sul**

## Curso de ENGENHARIA FÍSICA

Trabalho de Conclusão de Curso

Geração e Controle de Pulses de Radiofrequência para

um Protótipo de Imagem por Ressonância Magnética

***Jhoenne Helena Vasconcelos Pulcherio***

**Orientador:** Prof. Dr. Renan Albuquerque Marks

**Coorientador:** Pedro Henrique Andrade Trindade

Trabalho de Conclusão de Curso apresentado ao curso de Engenharia Física do Instituto de Física (INFI), da Universidade Federal de Mato Grosso do Sul (UFMS).

Campo Grande – MS

Dezembro/2025

## AGRADECIMENTOS

Agradeço à minha família, por todo amor, apoio e incentivo nesta etapa da minha vida. Em especial à minha mãe, Juliene Cristina de Vasconcelos, que sempre me acolheu, me motivou nos momentos difíceis e nunca mediu esforços para que eu alcançasse meus objetivos. Aos meus avós, Aparecida Helena Pavesi Vasconcelos e Pedro Saturnino de Vasconcelos, que foram um grande suporte e me ajudaram a chegar até aqui. E ao meu irmão, João Pedro Vasconcelos Pulcherio, pela presença e companheirismo em todo o processo.

Ao meu orientador, Prof. Dr. Renan Albuquerque Marks, pela disponibilidade e orientação ao longo deste trabalho. Ao meu coorientador, Pedro Henrique Andrade Trindade, pelos ensinamentos, paciência e conselhos. Agradeço a todos os meus colegas do Centro Nacional de Pesquisa em Energia e Materiais (CNPEM), em especial aos grupos de Eletrônica e Sistemas Embaçados e de Arquitetura e Modelagem de Sistemas, pelos aprendizados, apoio e pela convivência no dia a dia. Às minhas antigas supervisoras, Marisa Fonseca e Maria Eduarda Tempesta, pelo acolhimento e incentivo no primeiro ano de estágio. Às minhas amigas Aline, Letícia e Paula, pelas conversas, risadas e apoio em todos os momentos.

Aos meus amigos da Universidade Federal de Mato Grosso do Sul (UFMS), em especial ao Guilherme Costa, pelo apoio, incentivo e amizade que ajudaram a tornar essa jornada mais leve. Também aos amigos Felipe, Pedro e Rayane, pelo companheirismo ao longo de toda a graduação. Sem vocês, esse processo teria sido muito mais difícil. Ao Grupo de Óptica e Fotônica (GOF), onde fui bolsista durante grande parte da graduação, agradeço pelos aprendizados, pelas conversas e pelos cafés da tarde.

À República Danoninho, que se tornou um lar nos últimos dois anos, em especial à Emanuele Dória e ao Breno Porto, pela compreensão, apoio e por todos os momentos de conversa e descontração.

Ao CNPEM, pela oportunidade de estágio e pela bolsa concedida. Agradeço também ao Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq) e ao Programa de Auxílio Permanência da UFMS, pelo apoio financeiro que possibilitou cursar a graduação em tempo integral.

Por fim, agradeço a todos que, de alguma forma, contribuíram para a realização deste trabalho e para a minha formação pessoal e profissional. Sem vocês, eu não teria chegado até aqui.

## RESUMO

A Ressonância Magnética (RM) é uma técnica de diagnóstico por imagem não invasiva e de alta resolução, amplamente utilizada na medicina por permitir a diferenciação de tecidos sem o uso de radiação ionizante. No entanto, há uma desigualdade relevante entre o acesso a esses equipamentos em função da região no Brasil, que apresenta áreas extensas com oferta baixa ou inexistente desses exames. O desenvolvimento de equipamentos nacionais de RM representa uma alternativa para reduzir custos e ampliar o acesso, promovendo autonomia tecnológica. Considerando esse contexto, o CNPEM está desenvolvendo competências nesse campo e, atualmente conta com um protótipo de RM de 0,4 T desenvolvido parcialmente no centro, com exceção de amplificadores de gradiente, amplificadores de potência e console. O presente trabalho marca o início do desenvolvimento de um console, com foco no sistema de transmissão de sinais de Radiofrequência (RF). O objetivo foi desenvolver e validar um gerador digital de pulsos de RF, implementado em Field-Programmable Gate Array (FPGA), utilizando a placa de desenvolvimento Red Pitaya e a linguagem de descrição de hardware VHSIC Hardware Description Language (VHDL). A metodologia empregou a técnica de Síntese Digital Direta (Direct Digital Synthesis (DDS)) para a geração de portadoras senoidais e cosenoïdais por meio de um Oscilador Controlado Numericamente (Numerically Controlled Oscillator (NCO)), em conjunto com a modulação em quadratura (IQ). O projeto digital foi desenvolvido em VHDL e validado através de *testbenches* em ambiente de simulação no software Vivado. Os resultados das simulações mostraram o correto funcionamento da integração dos módulos e a geração do pulso com a frequência de acordo com o parâmetro de controle. Esse comportamento validou a geração de sinais com controle de frequência a partir da técnica de DDS e a modulação do pulso. Os testes em bancada mostraram um pulso modulado no osciloscópio compatível com as simulações realizadas, confirmando a correta implementação em FPGA para a geração dos pulsos de RF, com valores experimentais próximos aos simulados. O trabalho contribuiu com a capacitação da equipe, servindo como uma etapa inicial no processo de desenvolvimento do console conceitual. Os resultados obtidos nesse processo podem ser otimizados e aprimorados de forma que, no futuro, contribuam para o objetivo do CNPEM de desenvolver um equipamento de RM integralmente nacional.

**Palavras-Chave:** Ressonância Magnética, Radiofrequência, FPGA, DDS, VHDL, Red Pitaya.

## ABSTRACT

Magnetic Resonance Imaging (MRI) is a non-invasive, high-resolution imaging technique widely used in medicine for its ability to differentiate soft tissues without the use of ionizing radiation. However, there is a significant inequality in access to such equipment across Brazil, with large regions showing limited or no availability of MRI exams. The development of national MRI equipment represents an alternative to reduce costs and expand access, promoting technological autonomy. In this context, the CNPEM has been developing expertise in this field and currently has a 0.4 T MRI prototype partially developed at the center, except for the gradient amplifiers, power amplifiers, and console. This work marks the beginning of the console development, focusing on the RF transmission system. The objective was to design and validate a digital RF pulse generator implemented on an FPGA, using the Red Pitaya development board and the VHDL hardware description language. The methodology employed the DDS technique for generating sine and cosine carriers through a NCO, combined with quadrature (IQ) modulation. The digital design was developed in VHDL and validated through *testbenches* in a simulation environment using Vivado software. Simulation results demonstrated the correct integration of the modules and the generation of the pulse with frequency matching the control parameter. This behavior validated the frequency-controlled signal generation using the DDS technique and pulse modulation. Bench tests showed a modulated pulse on the oscilloscope consistent with the simulations, confirming the correct FPGA implementation for RF pulse generation, with experimental values close to those obtained in simulation. This work contributed to the team's technical training and served as an initial step in the development of the conceptual console. The results obtained in this process can be further optimized and improved to support CNPEM's goal of developing a fully national MRI system in the future.

**Keywords:** Magnetic Resonance Imaging, Radiofrequency, FPGA, DDS, VHDL, Red Pitaya.

## Lista de Figuras

|    |                                                                                                                                                                                                                                           |    |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

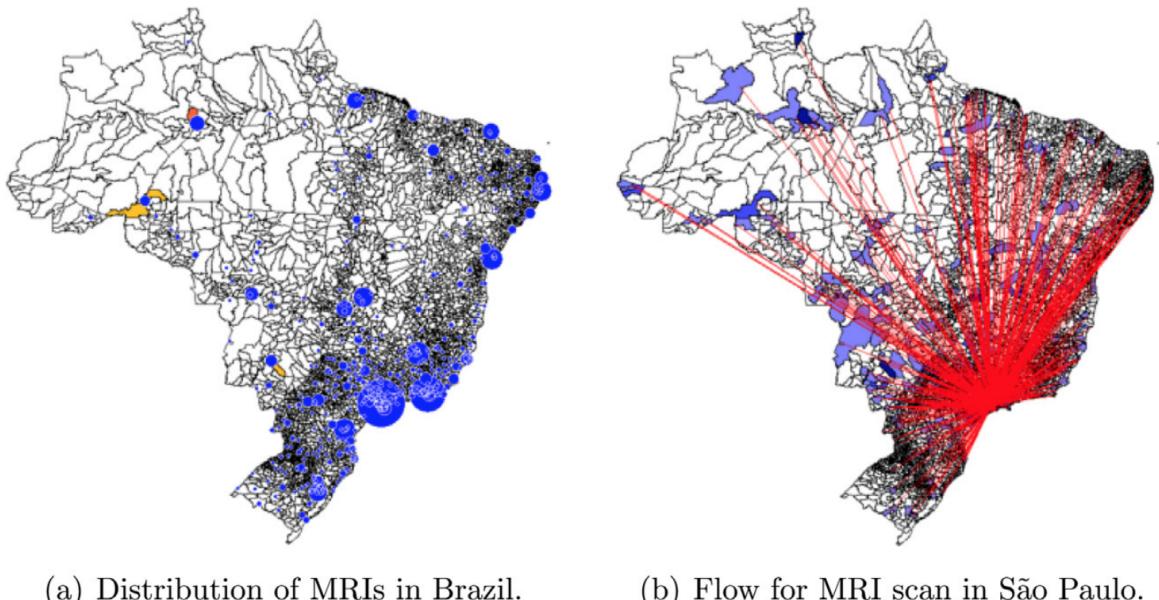

| 1  | Distribuição de equipamentos de MRI no Brasil, destacando: (a) desigualdade de acessibilidade dos exames no país e (b) fluxo para exames de MRI em São Paulo [2]. . . . .                                                                 | 12 |

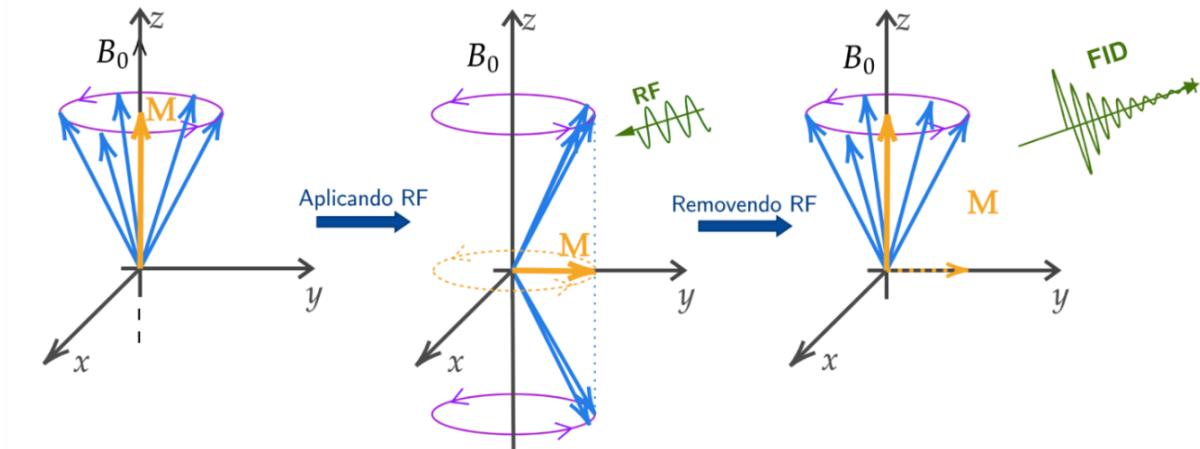

| 2  | Representação do fenômeno de ressonância magnética envolvendo pulso de RF para gerar a magnetização transversal e a geração do Free Induction Decay (FID) durante a relaxação [6]. . . . .                                                | 15 |

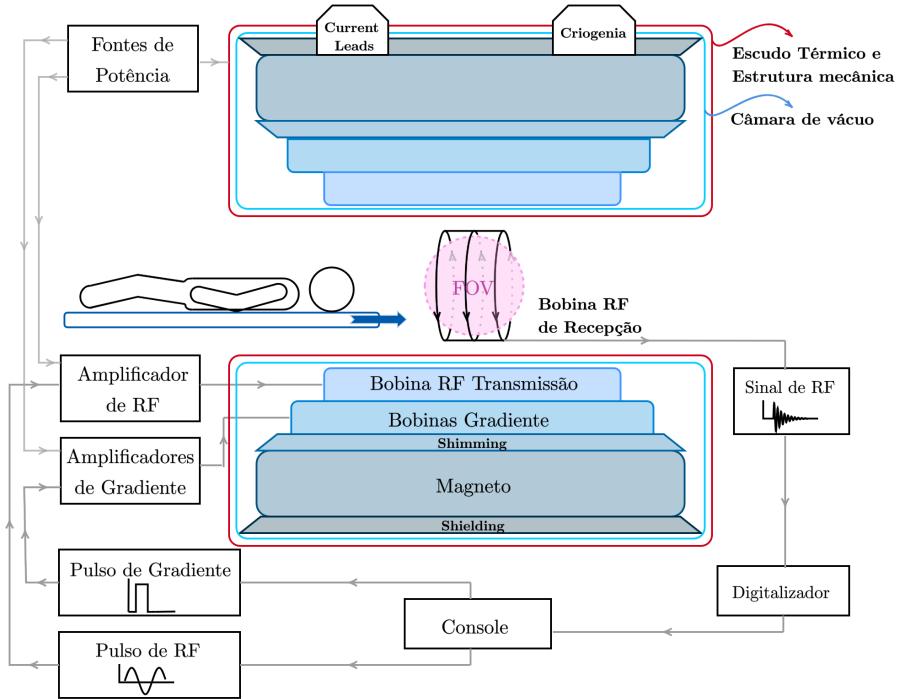

| 3  | Subsistemas de um equipamento de MRI tradicional com magneto do tipo supercondutor, que requer escudo térmico e câmara de vácuo para operação[6]. . .                                                                                     | 17 |

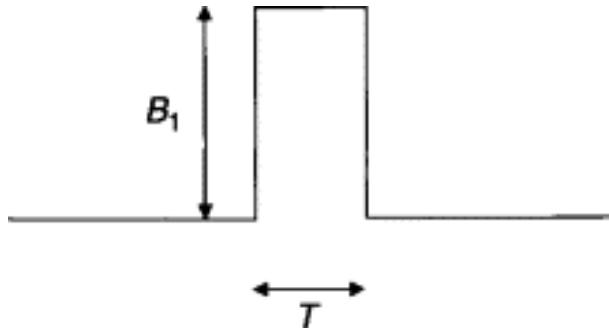

| 4  | Forma de onda de um pulso retangular (função <i>RECT</i> ) no domínio do tempo [8].                                                                                                                                                       | 18 |

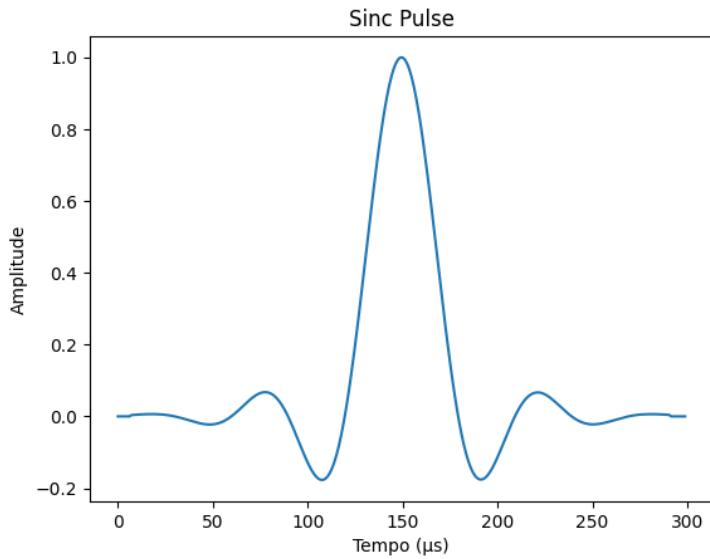

| 5  | Forma de onda de um pulso <i>sinc</i> no domínio do tempo. . . . .                                                                                                                                                                        | 19 |

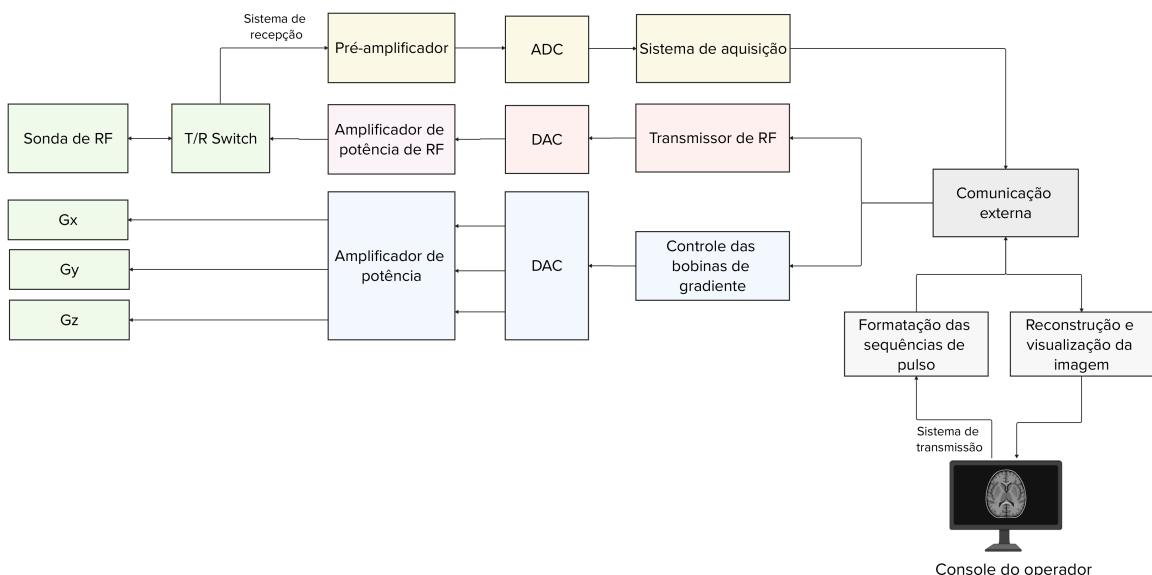

| 6  | Diagrama de blocos de um console de controle em ressonância magnética, ilustrando os fluxos de transmissão e recepção dos sinais. . . . .                                                                                                 | 21 |

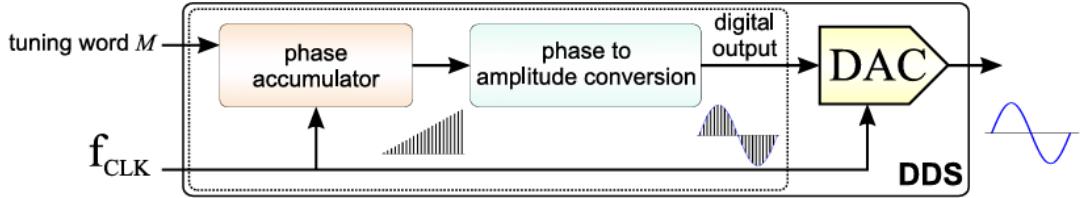

| 7  | Diagrama de um DDS contendo um NCO (linha tracejada) e Digital-to-Analog Converter (DAC) [13]. . . . .                                                                                                                                    | 23 |

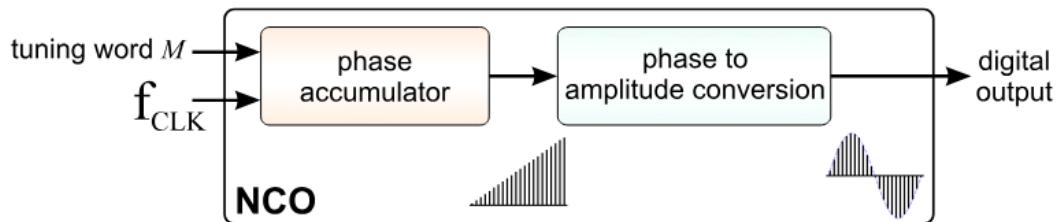

| 8  | Diagrama de um NCO com os módulos <i>phase accumulator</i> e <i>phase to amplitude conversion</i> [13]. . . . .                                                                                                                           | 23 |

| 9  | Placa comercial Red Pitaya 122-16. . . . .                                                                                                                                                                                                | 25 |

| 10 | Pulso <i>sinc</i> janelado com Hamming (250 amostras) gerado em Python. . . . .                                                                                                                                                           | 26 |

| 11 | Um período da onda senoidal gerada com 4096 amostras. . . . .                                                                                                                                                                             | 27 |

| 12 | Um quarto do período da onda senoidal gerada com 1024 amostras. . . . .                                                                                                                                                                   | 28 |

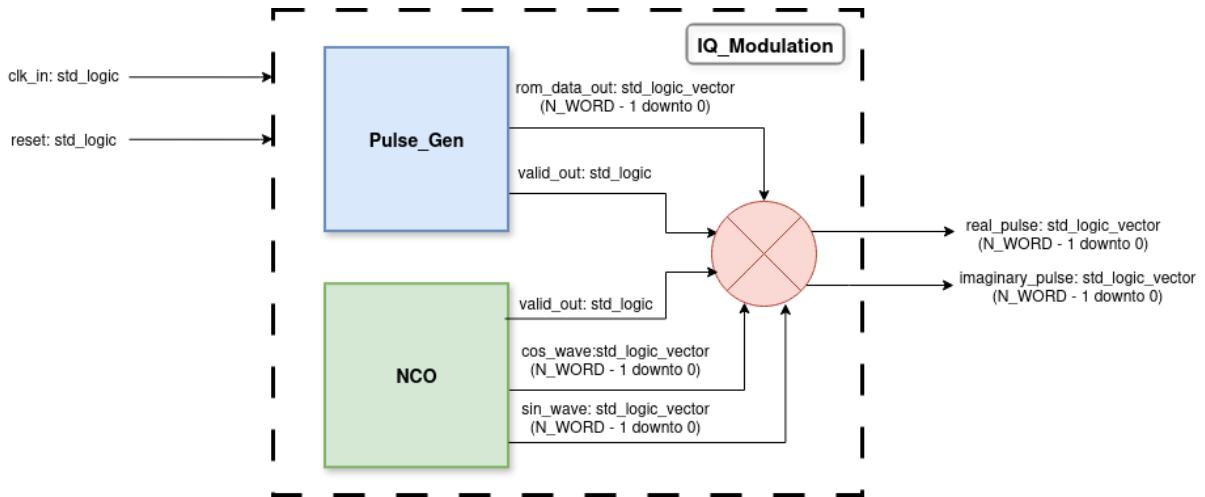

| 13 | Diagrama do módulo <b>IQ_Modulation</b> . O símbolo circular em vermelho representa a operação de multiplicação entre os sinais da envoltória gerada pelo <b>Pulse_Gen</b> e as portadoras senoidal e cossenoidal do <b>NCO</b> . . . . . | 30 |

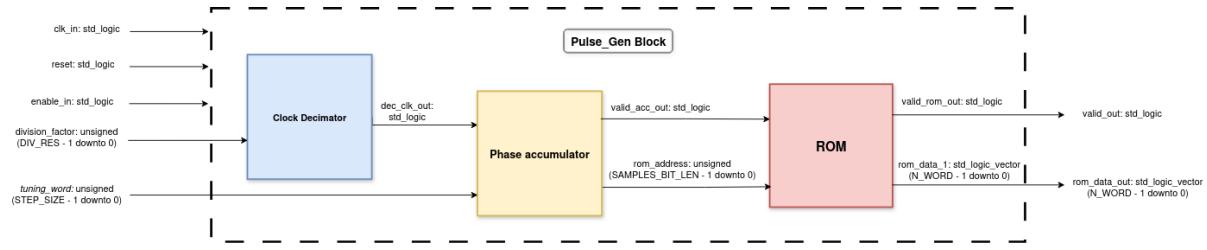

| 14 | Diagrama do módulo <b>Pulse_Gen</b> com os sinais de entrada e saída. . . . .                                                                                                                                                             | 31 |

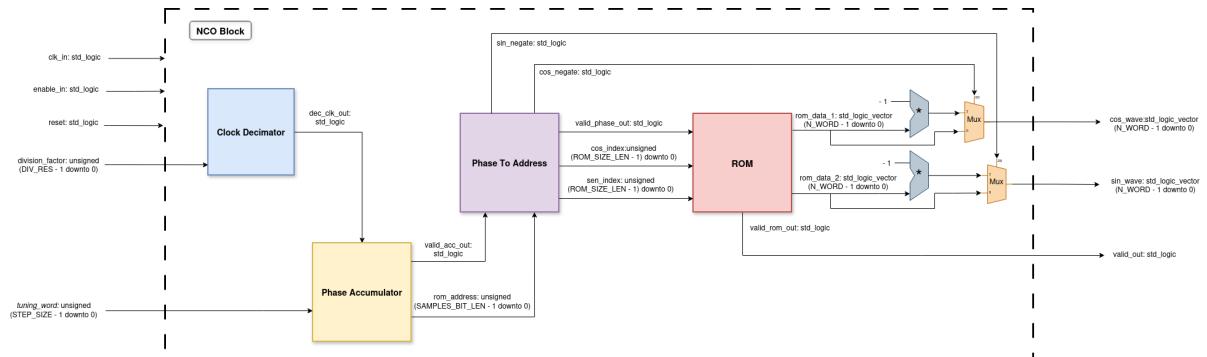

| 15 | Diagrama do módulo <b>NCO</b> com os sinais de entrada e saída. . . . .                                                                                                                                                                   | 32 |

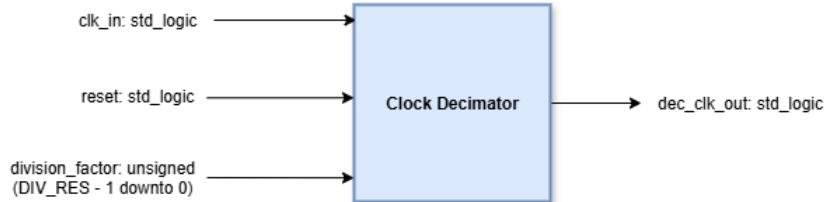

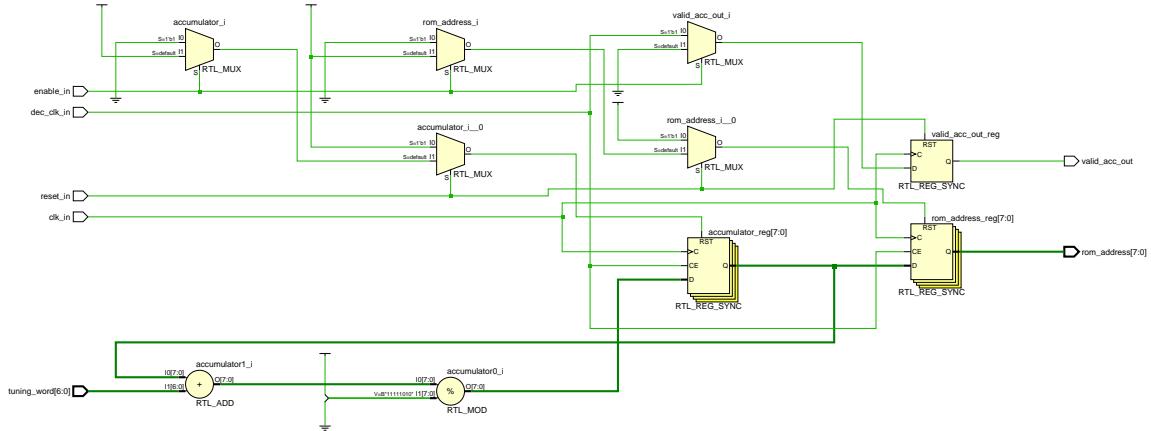

| 16 | Diagrama do módulo <b>C1k_Decimator</b> com os sinais de entrada e saída. . . . .                                                                                                                                                         | 33 |

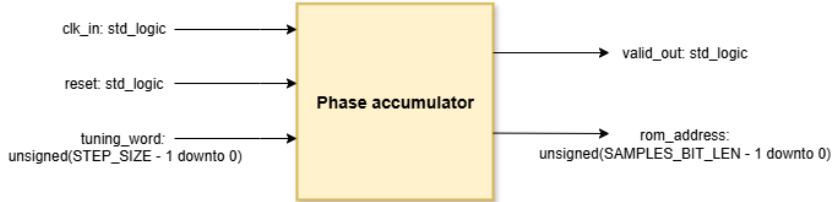

| 17 | Diagrama do módulo <b>Phase_Accumulator</b> com os sinais de entrada e saída. . . .                                                                                                                                                       | 34 |

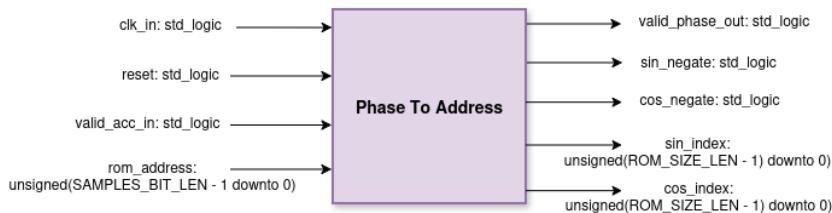

| 18 | Diagrama do módulo <b>Phase_to_Address</b> com os sinais de entrada e saída. . . .                                                                                                                                                        | 35 |

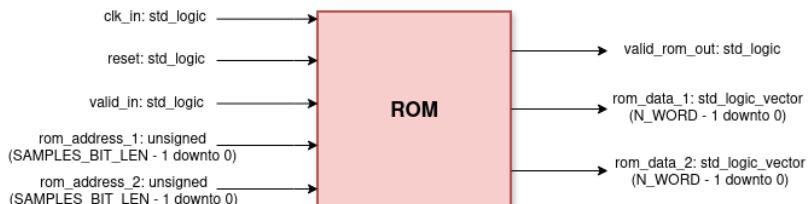

| 19 | Diagrama do módulo <b>ROM</b> com os sinais de entrada e saída para o uso no <b>NCO</b> . .                                                                                                                                               | 36 |

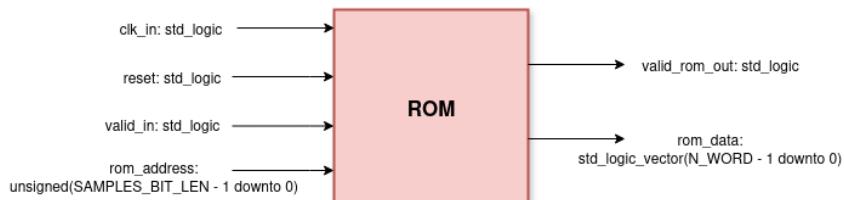

| 20 | Diagrama do módulo <b>ROM</b> com os sinais de entrada e saída para uso no <b>Pulse_Gen</b> . .                                                                                                                                           | 36 |

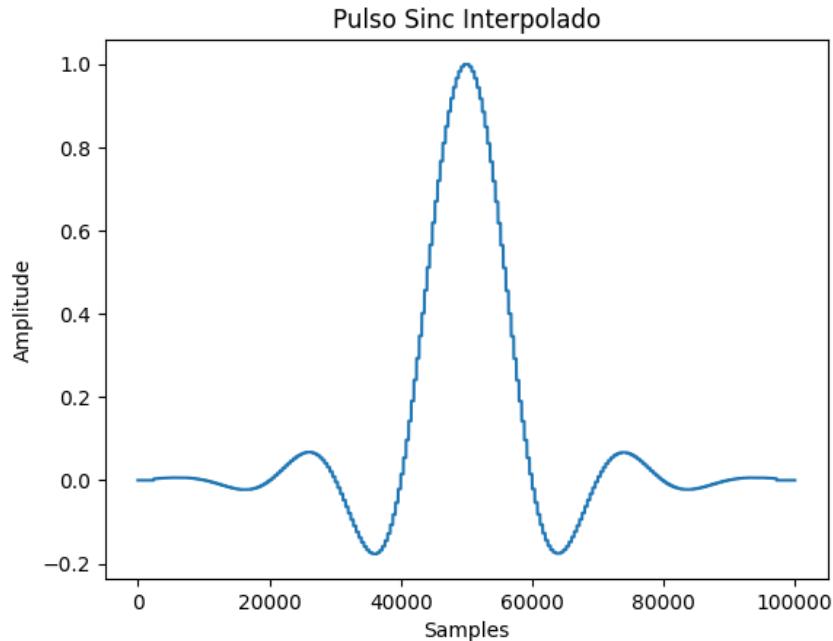

| 21 | Pulso <i>sinc</i> com 100.000 amostras. . . . .                                                                                                                                                                                           | 39 |

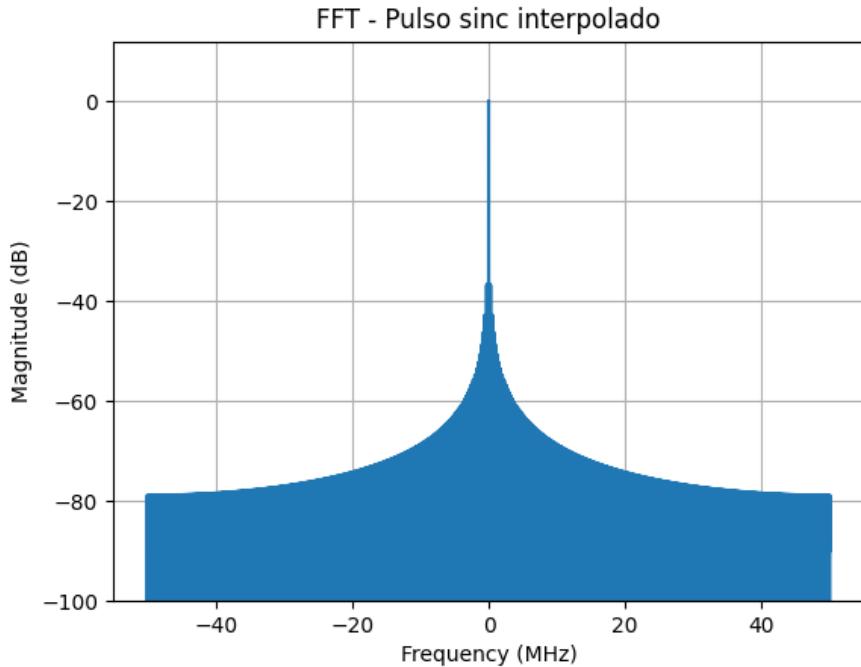

| 22 | Espectro de magnitude (Discrete Fourier Transform (DFT)) do pulso <i>sinc</i> interpolado. . . . .                                                                                                                                        | 40 |

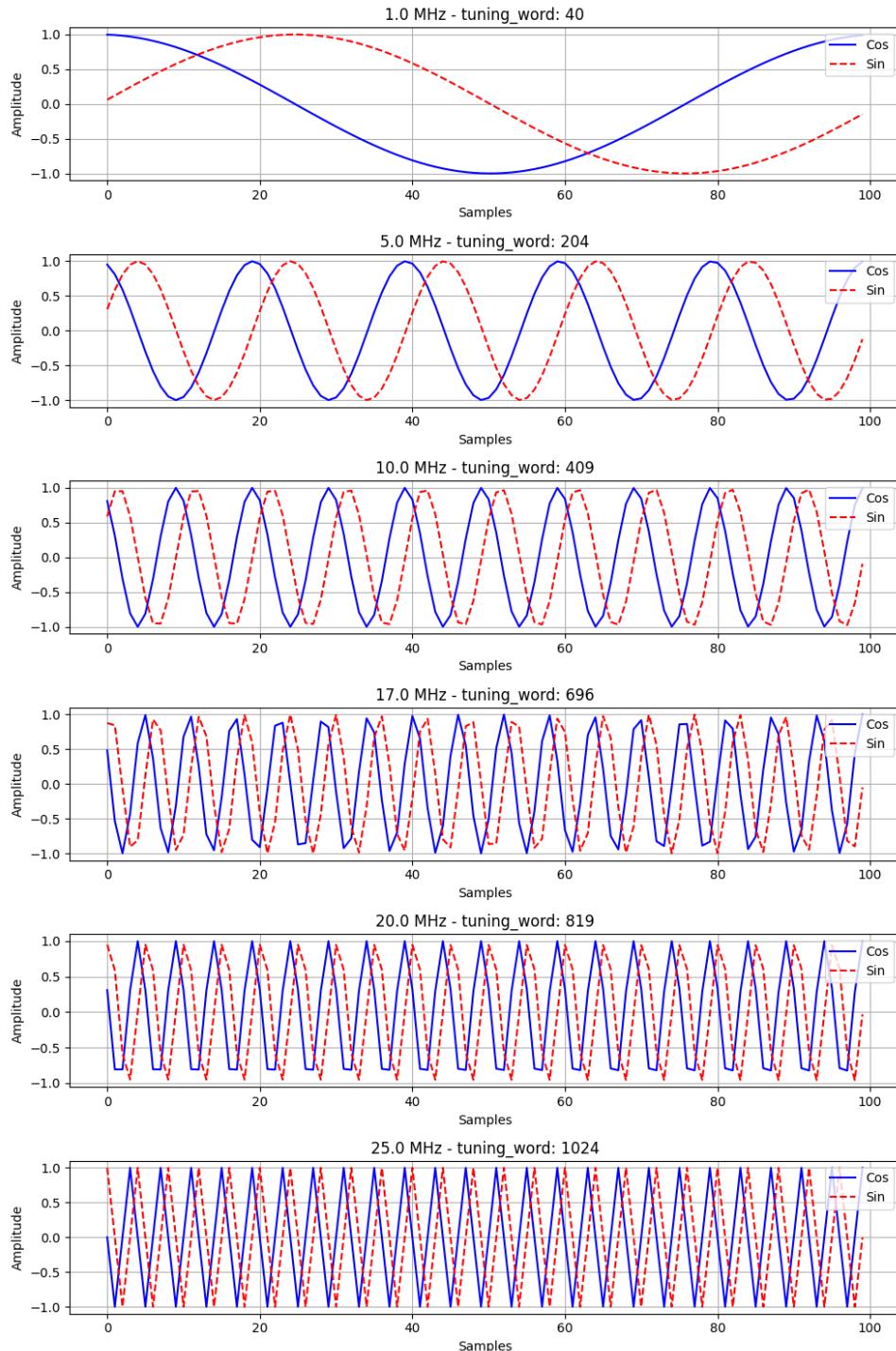

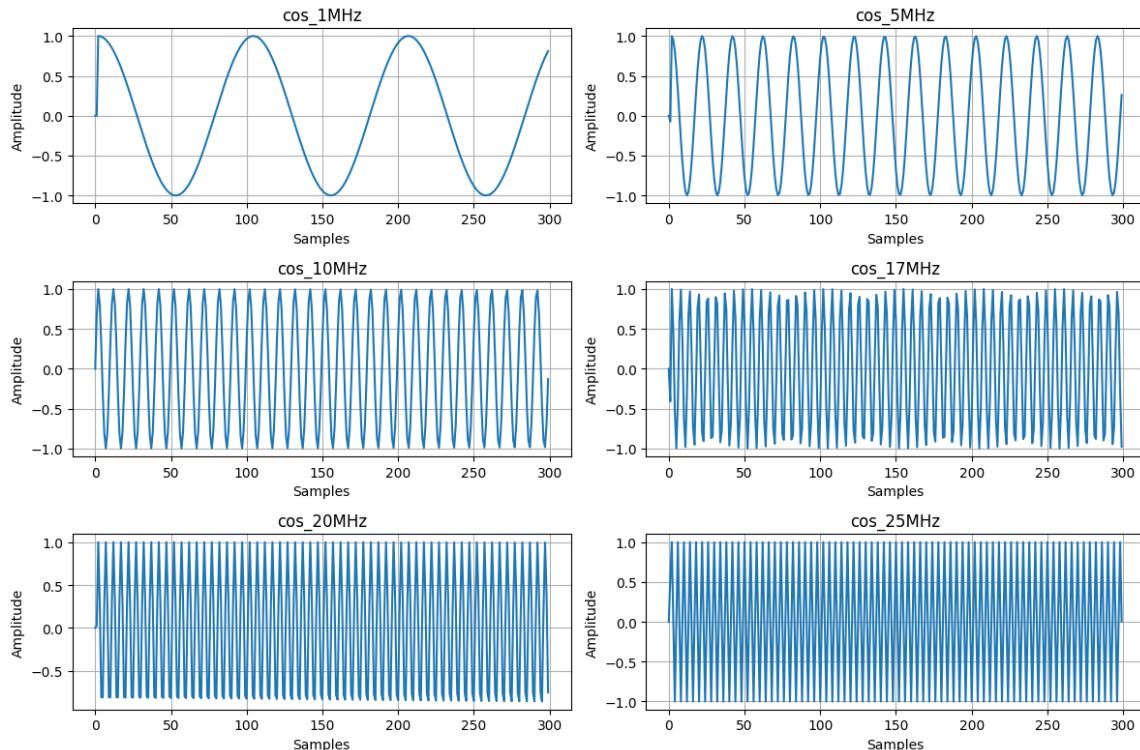

| 23 | Formas de onda senoidal e cossenoidal geradas pelo <b>NCO</b> em diferentes frequências de saída. . . . .                                                                                                                                 | 41 |

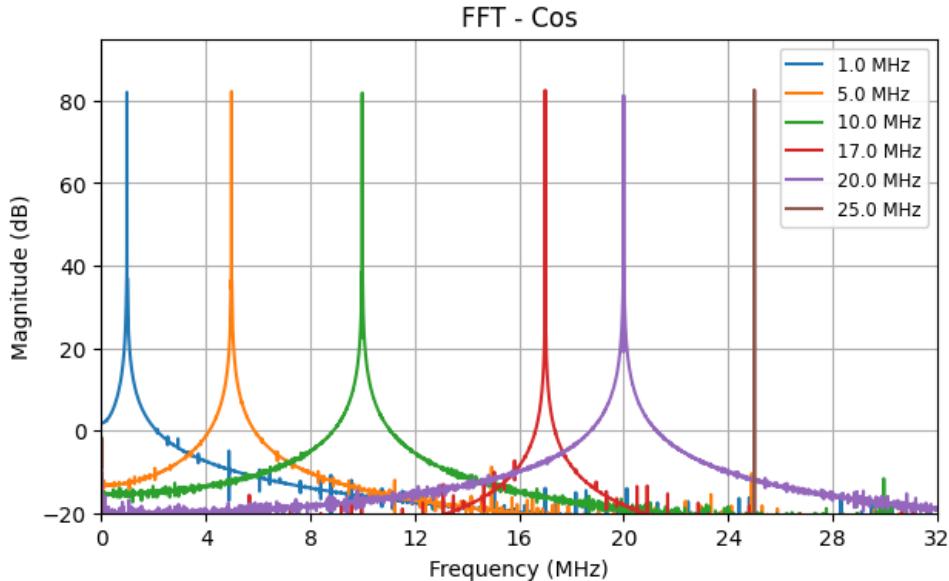

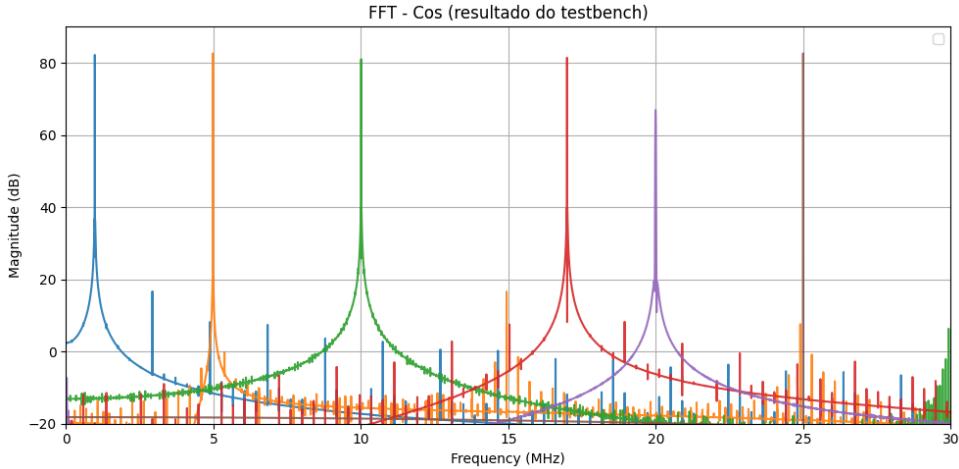

| 24 | Espectros de magnitude das ondas cossenoidais geradas pelo <b>NCO</b> para diferentes valores de <b>tuning_word</b> . . . . .                                                                                                             | 42 |

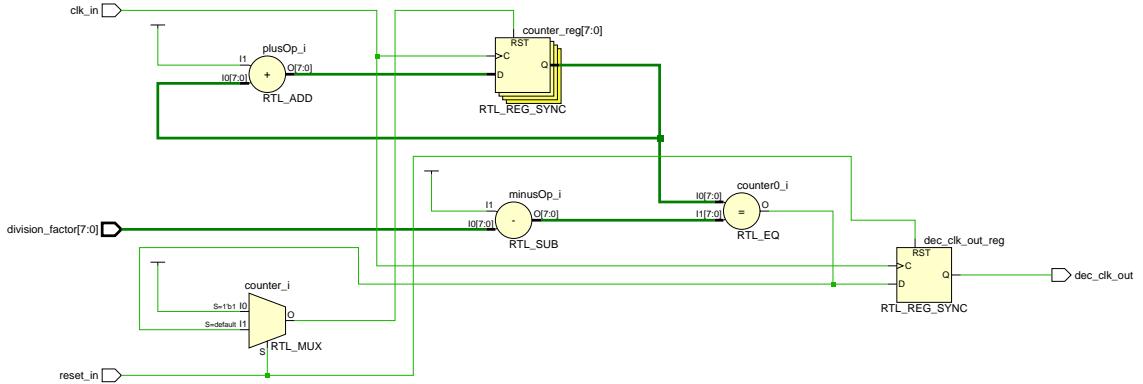

| 25 | Esquemático RTL do módulo <b>C1k_Decimator</b> gerado pelo Vivado. . . . .                                                                                                                                                                | 43 |

| 26 | Resultado da simulação do módulo <b>C1k_Decimator</b> no Vivado. . . . .                                                                                                                                                                  | 43 |

| 27 | Esquemático RTL do módulo <b>Phase_Accumulator</b> gerado pelo Vivado. . . . .                                                                                                                                                            | 44 |

| 28 | Resultado da simulação do módulo <b>Phase_Accumulator</b> no Vivado. . . . .                                                                                                                                                              | 44 |

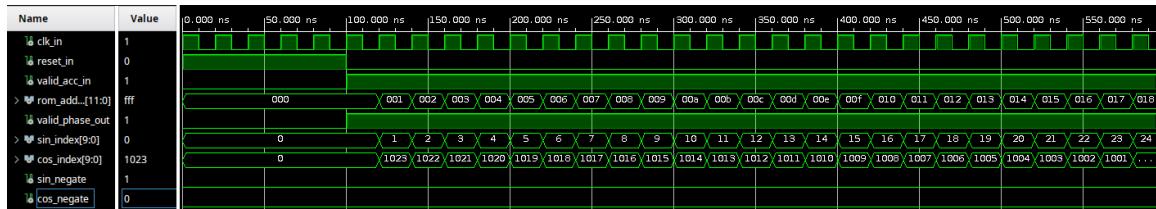

| 29 | Esquemático RTL do módulo <b>Phase_to_Address</b> gerado pelo Vivado. . . . .                                                                                                                                                             | 45 |

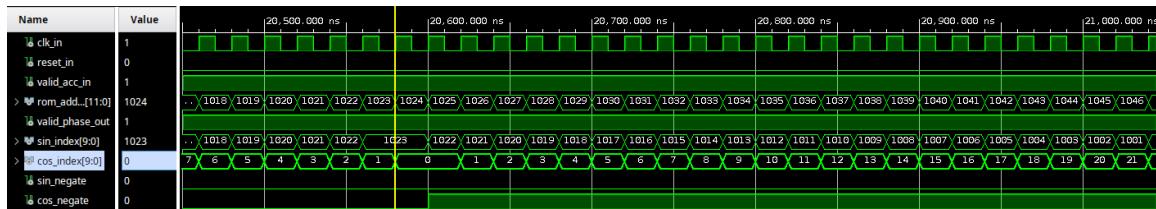

| 30 | Resultado da simulação do módulo <b>Phase_to_Address</b> no primeiro quadrante. .                                                                                                                                                         | 46 |

|    |                                                                                                                                                                                                                                                                                                                   |    |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 31 | Resultado da simulação do módulo <code>Phase_to_Address</code> na transição do primeiro para o segundo quadrante. . . . .                                                                                                                                                                                         | 46 |

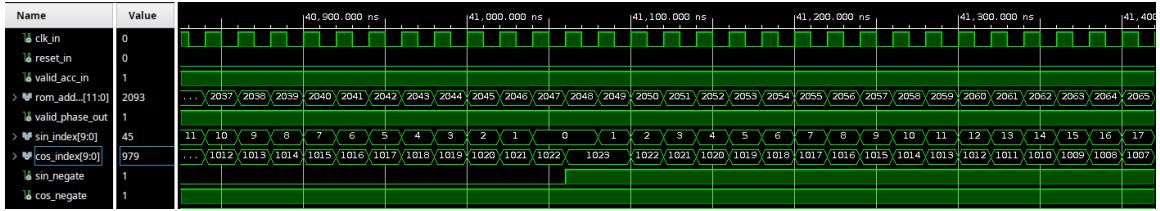

| 32 | Resultado da simulação do módulo <code>Phase_to_Address</code> na transição do segundo para o terceiro quadrante. . . . .                                                                                                                                                                                         | 47 |

| 33 | Resultado da simulação do módulo <code>Phase_to_Address</code> na transição do terceiro para o quadrante. . . . .                                                                                                                                                                                                 | 47 |

| 34 | Esquemático RTL do módulo <code>ROM</code> gerado pelo Vivado. . . . .                                                                                                                                                                                                                                            | 48 |

| 35 | Resultado da simulação do módulo <code>ROM</code> , mostrando a leitura sequencial das amostras do pulso. . . . .                                                                                                                                                                                                 | 48 |

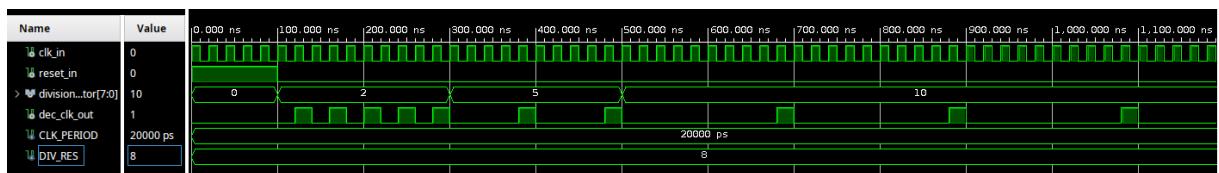

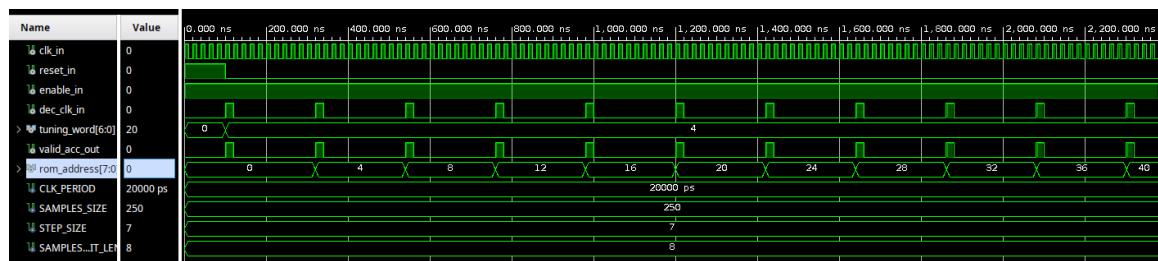

| 36 | Esquemático RTL do módulo <code>Pulse_Gen</code> com integração dos blocos <code>Clk_Decimator</code> , <code>Phase_Accumulator</code> e <code>ROM</code> . . . . .                                                                                                                                               | 49 |

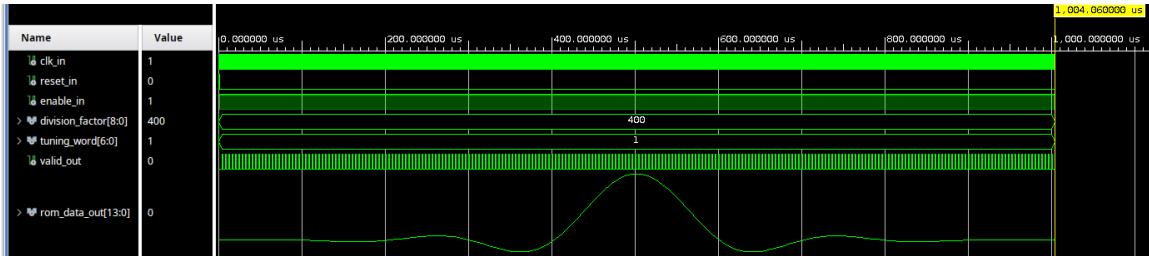

| 37 | Resultado da simulação do módulo <code>Pulse_Gen</code> mostrando a geração do pulso <i>sinc</i> com duração controlada. . . . .                                                                                                                                                                                  | 50 |

| 38 | Comparação entre o pulso gerado em VHDL e o vetor de teste obtido em Python. . . . .                                                                                                                                                                                                                              | 50 |

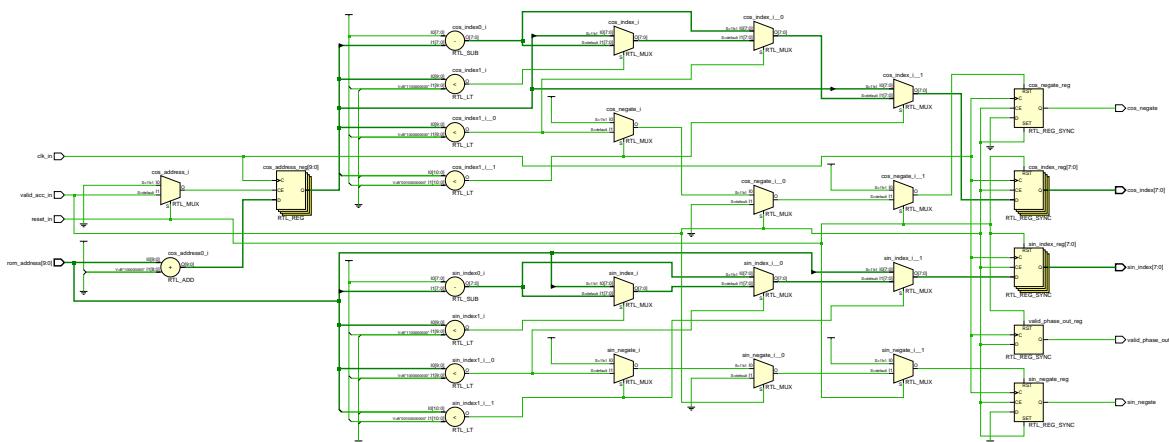

| 39 | Esquemático RTL do módulo <code>NCO</code> com integração dos blocos <code>Clk_Decimator</code> , <code>Phase_Accumulator</code> , <code>Phase_to_Address</code> e <code>ROM</code> . . . . .                                                                                                                     | 51 |

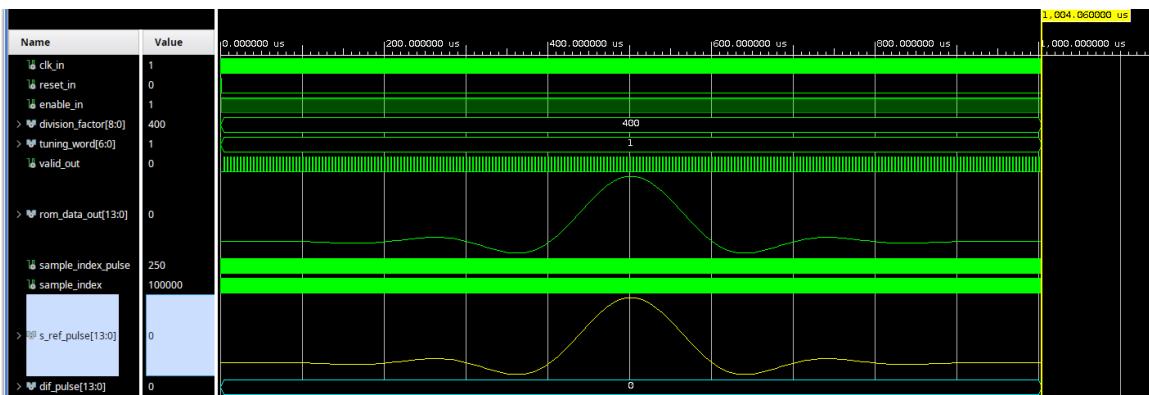

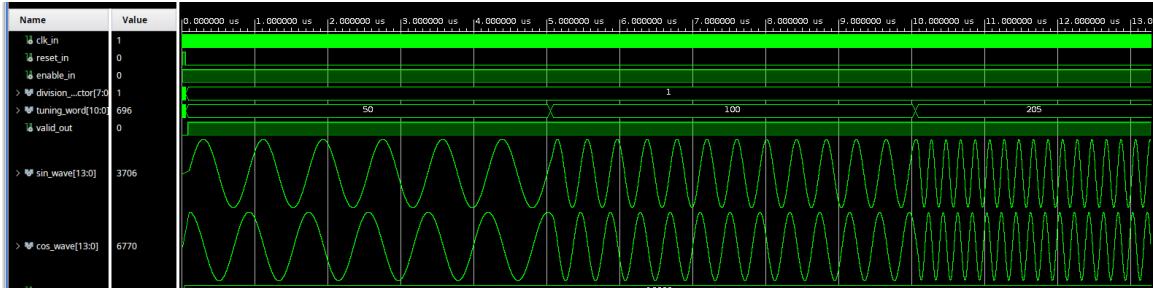

| 40 | Simulação do módulo <code>NCO</code> mostrando a defasagem de 90° entre as ondas senoidal e cossenoidal. . . . .                                                                                                                                                                                                  | 51 |

| 41 | Variação da frequência das portadoras conforme a mudança de <code>tuning_word</code> . . . . .                                                                                                                                                                                                                    | 52 |

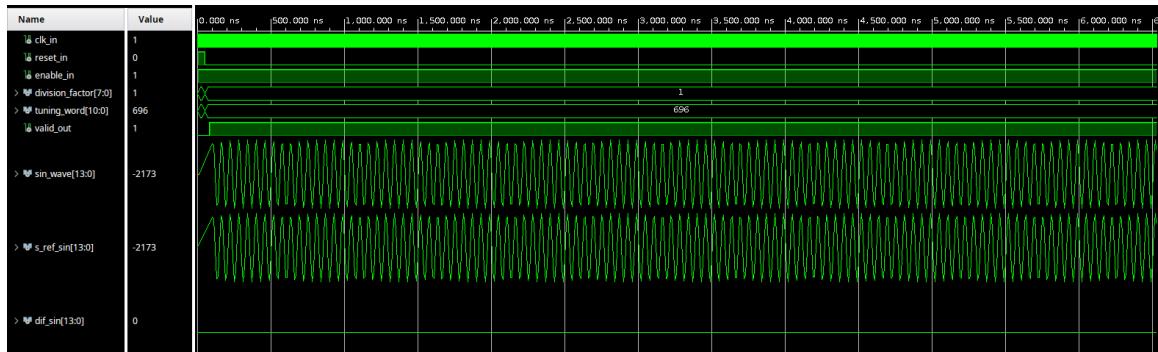

| 42 | Comparação entre a onda senoidal gerada em VHDL e o vetor de teste gerado em Python. . . . .                                                                                                                                                                                                                      | 52 |

| 43 | Comparação entre a onda cossenoidal gerada em VHDL e o vetor de teste gerado em Python. . . . .                                                                                                                                                                                                                   | 53 |

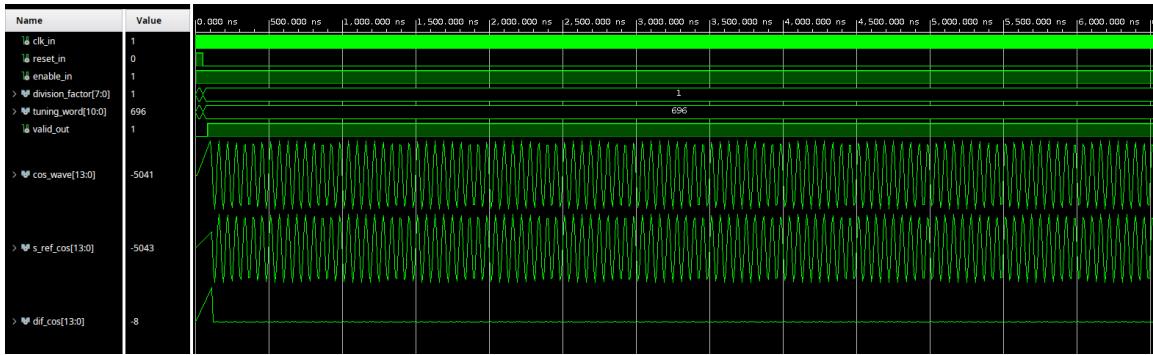

| 44 | Formas de onda cossenoidais reconstruídas em Python para diferentes valores de <code>tuning_word</code> . . . . .                                                                                                                                                                                                 | 53 |

| 45 | Espectros de magnitude das ondas cossenoidais geradas pelo <code>NCO</code> , mostrando picos nas frequências correspondentes aos valores de <code>tuning_word</code> . . . . .                                                                                                                                   | 54 |

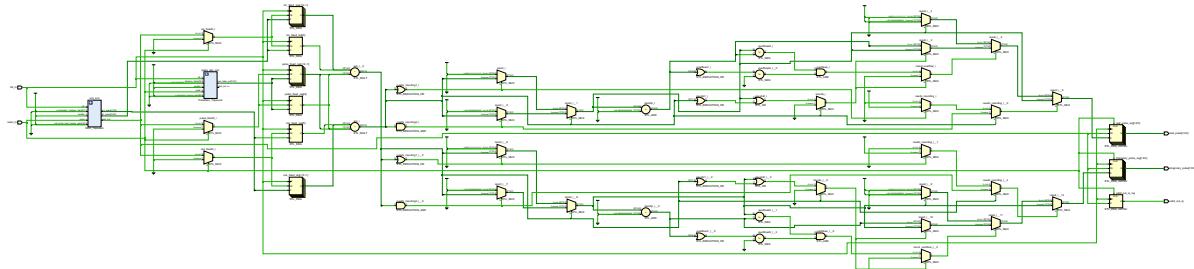

| 46 | Esquemático RTL do módulo <code>IQ_Modulation</code> com integração dos blocos <code>Pulse_Gen</code> e <code>NCO</code> . . . . .                                                                                                                                                                                | 55 |

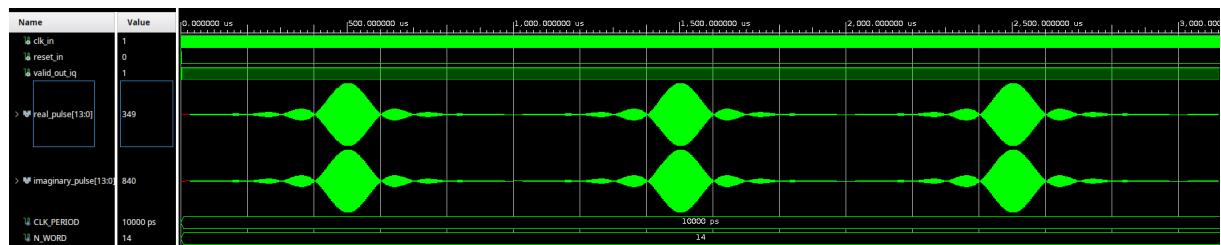

| 47 | Simulação do módulo <code>IQ_Modulation</code> mostrando as saídas <code>real_pulse</code> e <code>imaginary_pulse</code> . . . . .                                                                                                                                                                               | 55 |

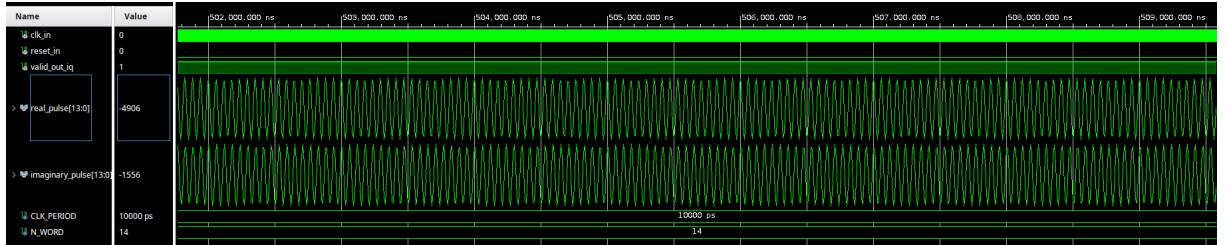

| 48 | Simulação com zoom da portadora modulada pela envoltória do pulso. . . . .                                                                                                                                                                                                                                        | 56 |

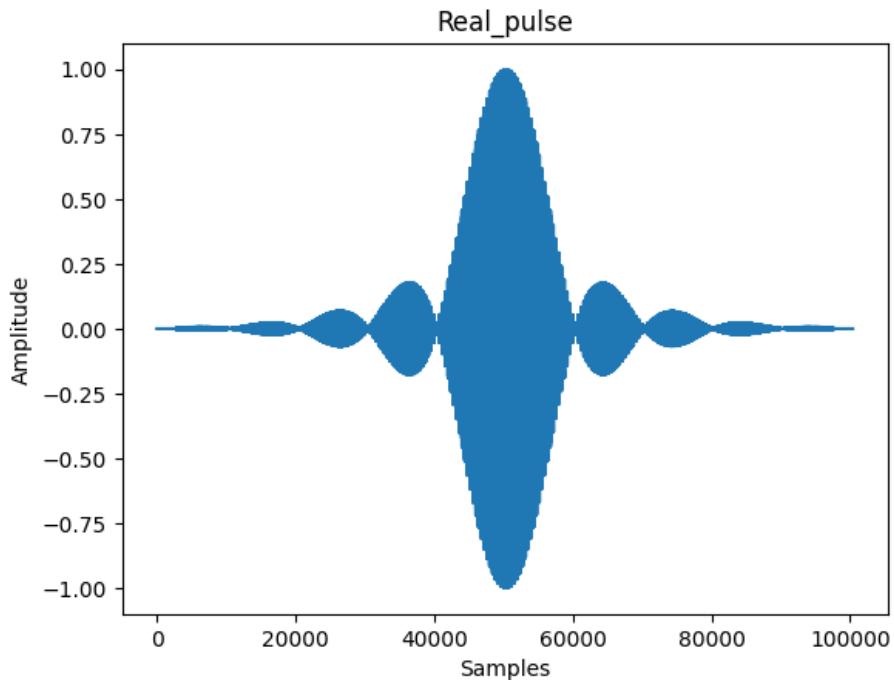

| 49 | Pulso reconstruído em Python a partir dos dados da saída <code>real_pulse</code> . . . . .                                                                                                                                                                                                                        | 56 |

| 50 | Espectro em frequência do pulso modulado ( <code>real_pulse</code> ), mostrando um pico em aproximadamente 17 MHz. . . . .                                                                                                                                                                                        | 57 |

| 51 | Relatório de Utilização de Recursos da FPGA (Pós-Síntese) para o módulo <code>IQ_Modulation</code> . As siglas representam os principais blocos internos da FPGA: LUT (Look-Up Table), FF (Flip-Flop), BRAM (Block RAM), DSP (Digital Signal Processor), IO (entradas e saídas) e BUFG (Buffer de clock). . . . . | 57 |

| 52 | Montagem experimental utilizada para validação do pulso gerado na FPGA. . . . .                                                                                                                                                                                                                                   | 58 |

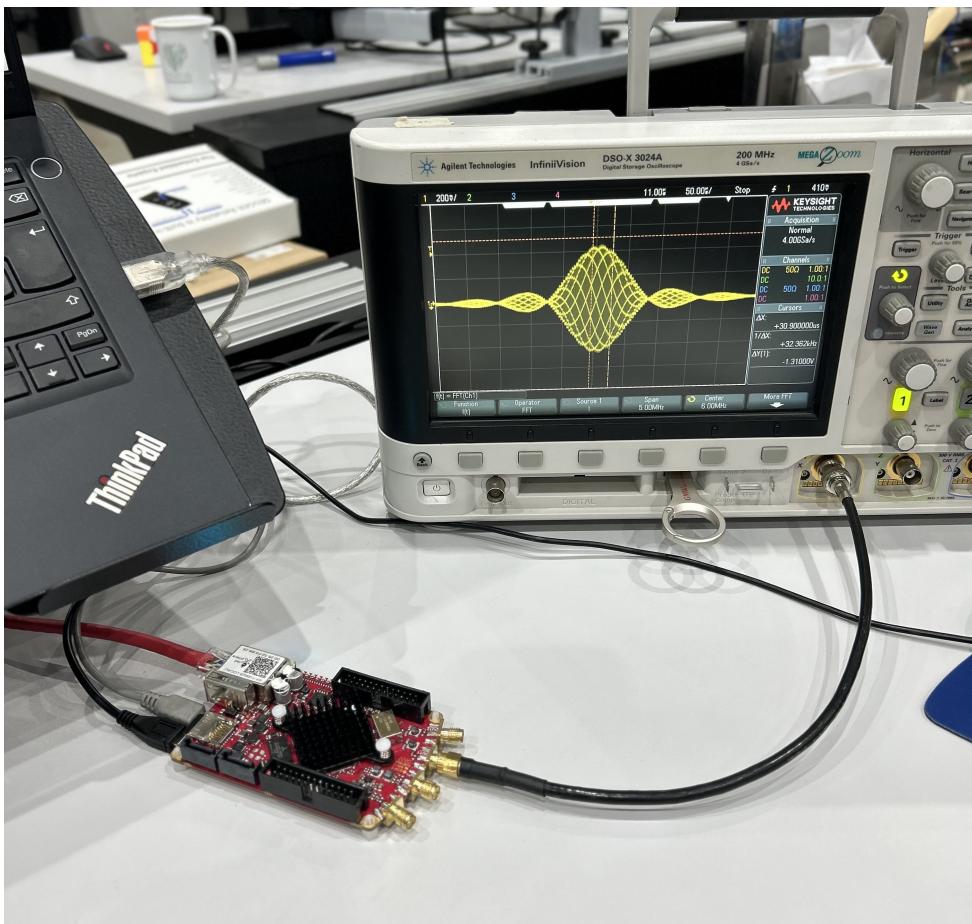

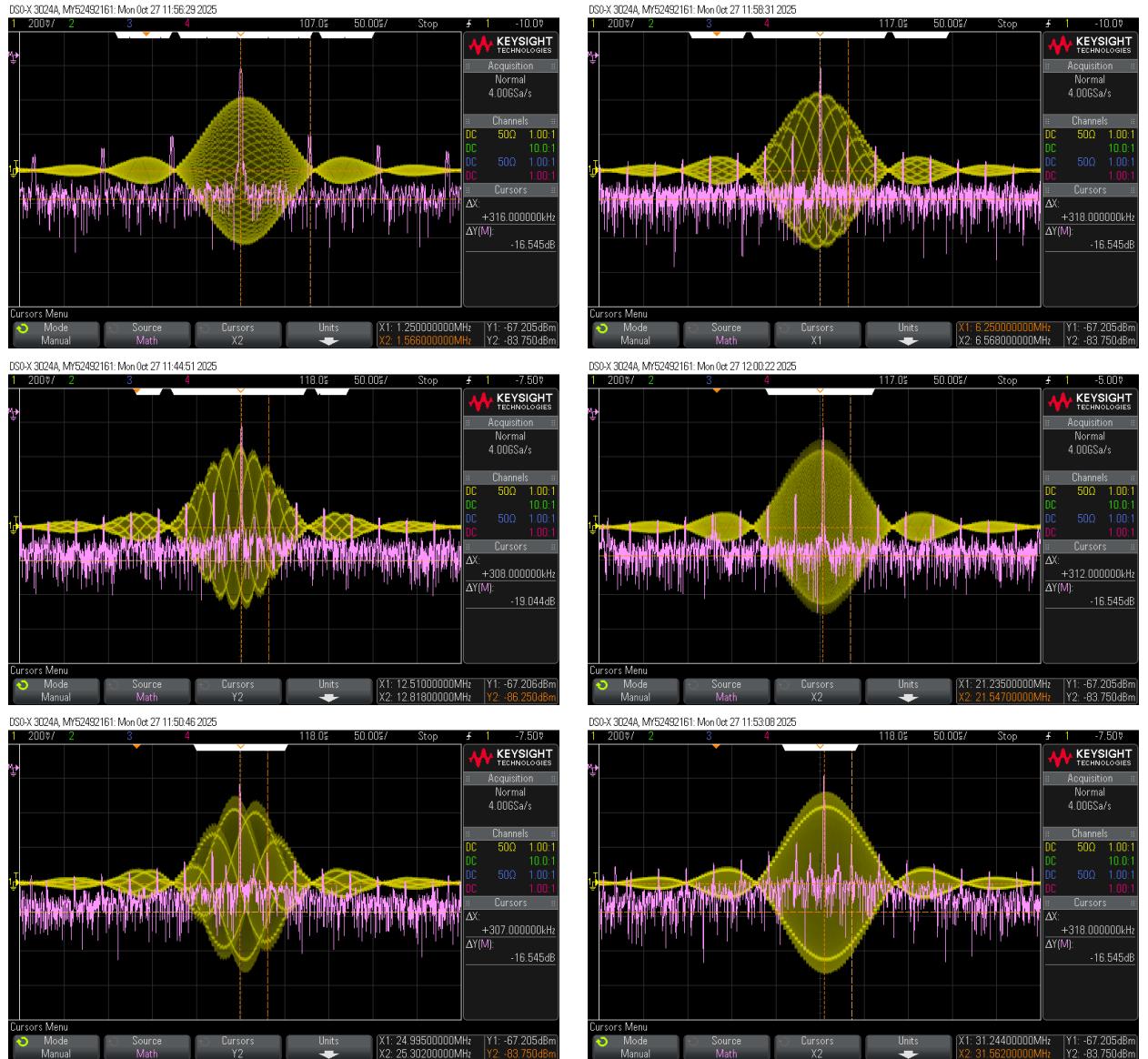

| 53 | Pulsos modulados observados no osciloscópio para os valores de <code>tuning_word</code> de 41, 205, 410, 696, 819, 1024. . . . .                                                                                                                                                                                  | 59 |

| 54 | Espectros dos pulsos modulados observados no osciloscópio para os valores de <code>tuning_word</code> de 41, 205, 410, 696, 819, 1024. . . . .                                                                                                                                                                    | 60 |

|    |                                                                                                                                                                      |    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

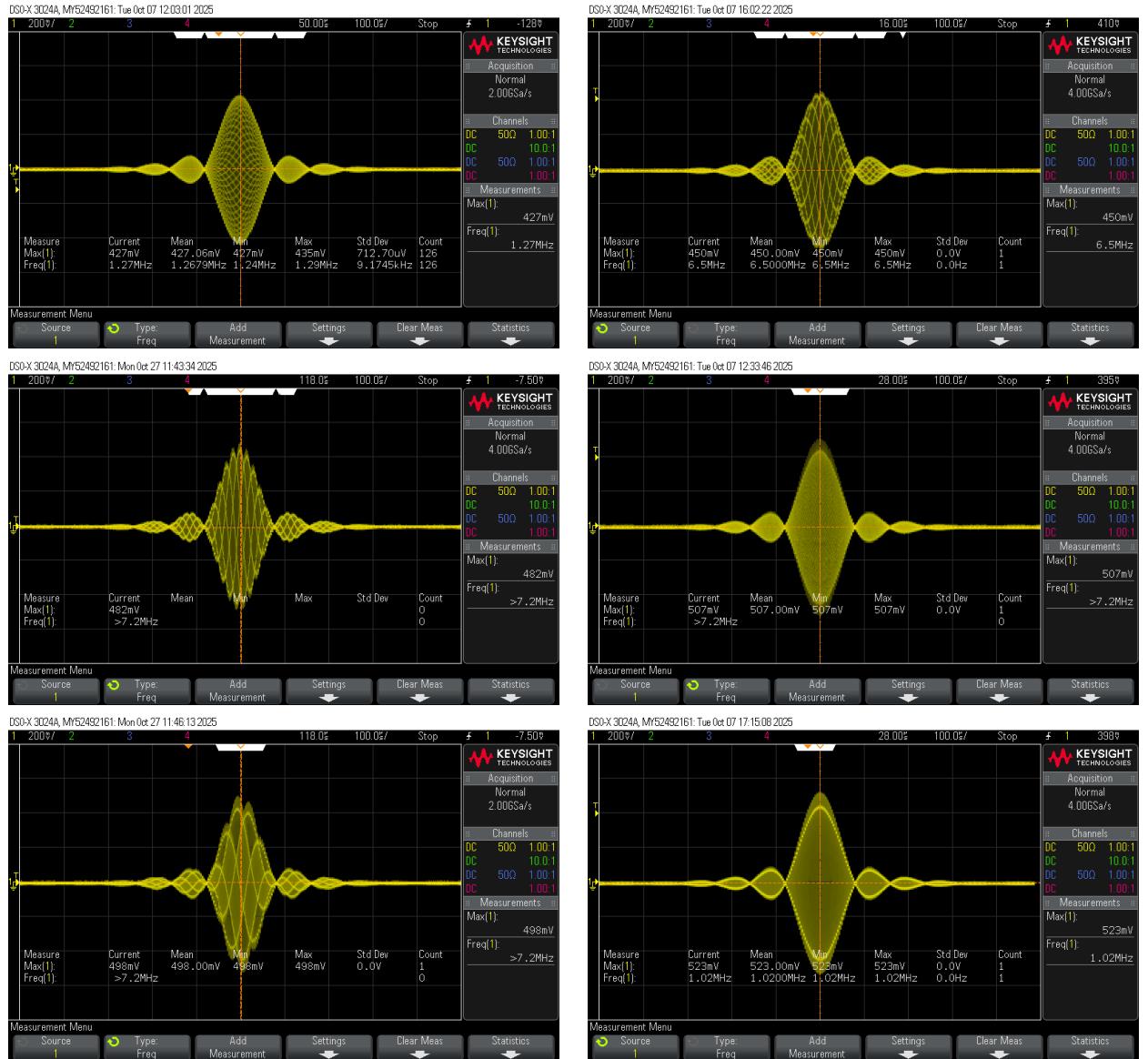

| 55 | Pulso modulado observado no osciloscópio para <code>tuning_word</code> = 558, correspondente à frequência de 17 MHz. . . . .                                         | 61 |

| 56 | Espectro (Fast Fourier Transform (FFT)) do pulso modulado observado no osciloscópio para <code>tuning_word</code> = 558, com pico em aproximadamente 17 MHz. . . . . | 62 |

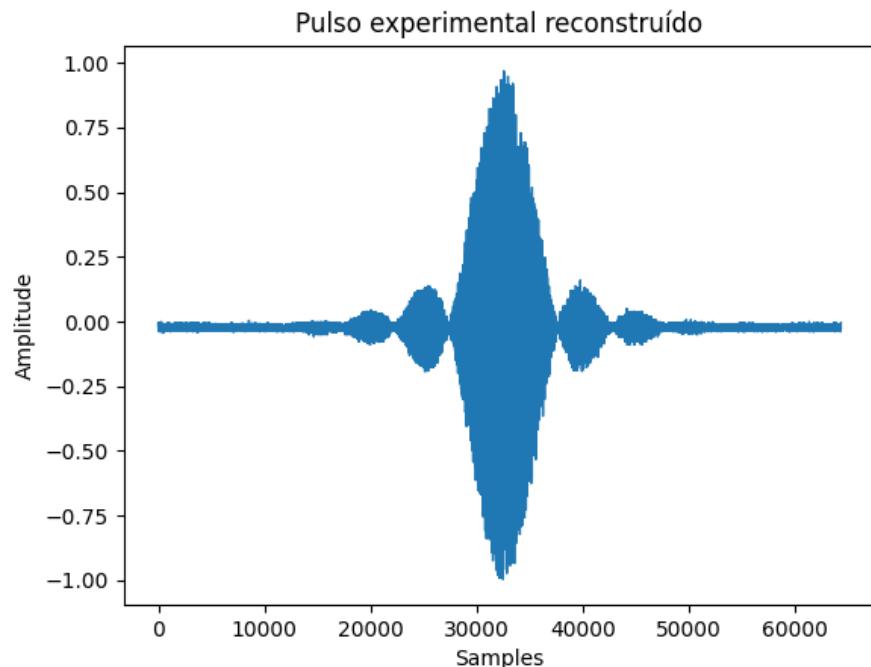

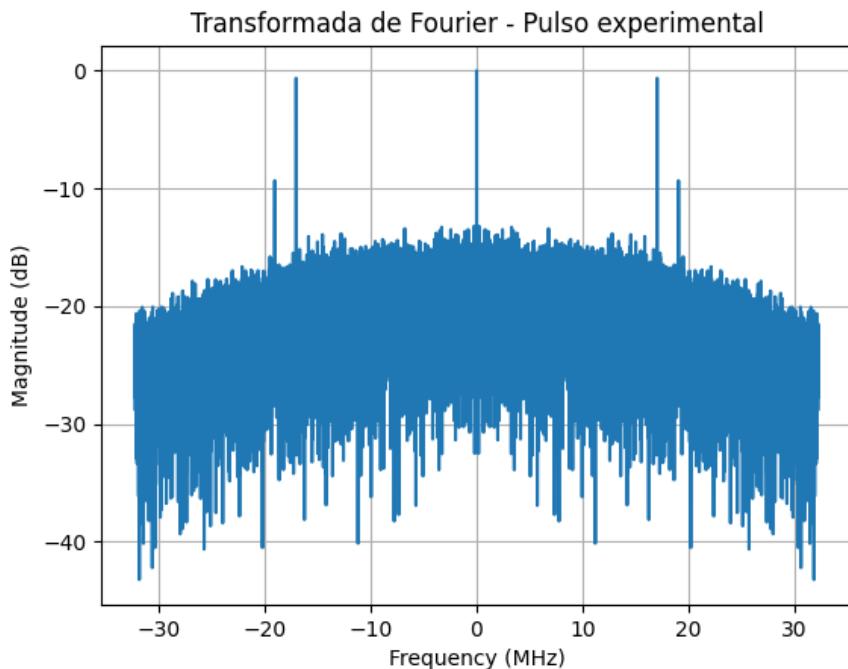

| 57 | Pulso reconstruído em Python a partir dos dados adquiridos no osciloscópio. . . . .                                                                                  | 62 |

| 58 | Espectro de magnitude do pulso reconstruído em Python a partir dos dados adquiridos no osciloscópio. . . . .                                                         | 63 |

## **Lista de Tabelas**

- 1      Comparação entre valores teóricos e medidos para diferentes `tuning_word`.    61

## Siglas

**ADC** Analog-to-Digital Converter.

**CNPSEM** Centro Nacional de Pesquisa em Energia e Materiais.

**DAC** Digital-to-Analog Converter.

**DDS** Direct Digital Synthesis.

**DFT** Discrete Fourier Transform.

**DUT** Device Under Test.

**FFT** Fast Fourier Transform.

**FID** Free Induction Decay.

**FPGA** Field-Programmable Gate Array.

**GPA** Gradient Power Amplifier.

**IRM** Imagem por Ressonância Magnética.

**MRI** Magnetic Resonance Imaging.

**NCO** Numerically Controlled Oscillator.

**RF** Radiofrequência.

**RM** Ressonância Magnética.

**RMN** Ressonância Magnética Nuclear.

**SLR** Shinnar-Le Roux.

**VHDL** VHSIC Hardware Description Language.

# Sumário

|          |                                                                         |           |

|----------|-------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>INTRODUÇÃO</b>                                                       | <b>12</b> |

| <b>2</b> | <b>OBJETIVOS</b>                                                        | <b>13</b> |

| 2.1      | Objetivo Geral . . . . .                                                | 13        |

| 2.2      | Objetivos Específicos . . . . .                                         | 13        |

| <b>3</b> | <b>FUNDAMENTAÇÃO TEÓRICA</b>                                            | <b>14</b> |

| 3.1      | Ressonância Magnética Nuclear (RMN) . . . . .                           | 14        |

| 3.1.1    | Fenômeno de RMN . . . . .                                               | 14        |

| 3.1.2    | Componentes de um equipamento de MRI . . . . .                          | 16        |

| 3.1.3    | Pulsos de Radiofrequência em RM . . . . .                               | 17        |

| 3.2      | Console de Controle . . . . .                                           | 20        |

| 3.3      | Processamento Digital de Sinais de RF . . . . .                         | 22        |

| 3.3.1    | Modulação <i>IQ</i> . . . . .                                           | 22        |

| 3.3.2    | Geração de Pulsos de RF . . . . .                                       | 22        |

| <b>4</b> | <b>METODOLOGIA</b>                                                      | <b>24</b> |

| 4.1      | Requisitos e Especificações do Sistema . . . . .                        | 25        |

| 4.2      | Geração de Pulsos de RF em Python e Conversão para Ponto Fixo . . . . . | 25        |

| 4.3      | Geração de Um Quarto da Onda Senoidal . . . . .                         | 27        |

| 4.4      | Simulação do comportamento do NCO em Python . . . . .                   | 28        |

| 4.5      | Implementação em VHDL . . . . .                                         | 29        |

| 4.5.1    | Modulação IQ ( <i>IQ_Modulation</i> ) . . . . .                         | 29        |

| 4.5.2    | Gerador de Pulso ( <i>Pulse_Gen</i> ) . . . . .                         | 30        |

| 4.5.3    | Gerador das Portadoras (NCO) . . . . .                                  | 31        |

| 4.6      | Módulos Básicos e Reutilizáveis . . . . .                               | 32        |

| 4.6.1    | Clock Decimator ( <i>Clk_Decimator</i> ) . . . . .                      | 32        |

| 4.6.2    | Phase Accumulator ( <i>Phase_Accumulator</i> ) . . . . .                | 33        |

| 4.6.3    | Phase to Address ( <i>Phase_to_Address</i> ) . . . . .                  | 34        |

| 4.6.4    | ROM (Read-Only Memory) . . . . .                                        | 36        |

| 4.7      | Metodologia de Validação dos Módulos em VHDL . . . . .                  | 37        |

| 4.8      | Validação Experimental em Bancada com Osciloscópio . . . . .            | 37        |

| <b>5</b> | <b>Resultados e Discussão</b>                                           | <b>38</b> |

| 5.1      | Largura de Banda do Pulso <i>Sinc</i> . . . . .                         | 38        |

| 5.2      | Simulação do NCO em Python . . . . .                                    | 40        |

| 5.3      | Validação dos Módulos Básicos e Reutilizáveis . . . . .                 | 42        |

| 5.3.1    | Clock Decimator ( <i>Clk_Decimator</i> ) . . . . .                      | 42        |

| 5.3.2    | Phase Accumulator ( <i>Phase_Accumulator</i> ) . . . . .                | 43        |

| 5.3.3    | Phase to Address ( <i>Phase_to_Address</i> ) . . . . .                  | 45        |

| 5.3.4    | ROM (Read-Only Memory) . . . . .                                        | 47        |

| 5.4      | Validação dos Módulos de Integração . . . . .                           | 49        |

| 5.4.1    | Gerador de Pulso ( <i>Pulse_Gen</i> ) . . . . .                         | 49        |

|          |                                                   |           |

|----------|---------------------------------------------------|-----------|

| 5.4.2    | Gerador das Portadoras (NCO) . . . . .            | 50        |

| 5.4.3    | Modulação IQ (IQ_Modulation) . . . . .            | 54        |

| 5.5      | Validação Experimental com Osciloscópio . . . . . | 58        |

| <b>6</b> | <b>CONCLUSÃO</b>                                  | <b>64</b> |

|          | <b>REFERÊNCIAS</b>                                | <b>65</b> |

# 1 INTRODUÇÃO

A RM é uma tecnologia capaz de fornecer diagnósticos por imagem com alta resolução espacial e capacidade de diferenciação de tecidos, podendo ser aplicada por toda a extensão do corpo humano [1]. Utilizando um campo magnético intenso, pulsos de RF e um sistema computacional, a Imagem por Ressonância Magnética (IRM) (em inglês, Magnetic Resonance Imaging, MRI) produz imagens detalhadas de órgãos internos, possibilitando diagnósticos precisos para uma ampla variedade de condições médicas [2]. Além disso, a técnica se destaca por não utilizar radiação ionizante, sendo considerada não invasiva e permitindo exames repetidos de forma segura [3]. No entanto, a disseminação e a disponibilidade equitativa dessa tecnologia representam um desafio significativo, especialmente em países em desenvolvimento como o Brasil. O cenário nacional revela uma distribuição de equipamentos de RM desigual. Dados de 2017 mostraram que apenas 462 dos 5569 municípios brasileiros possuíam esse tipo de equipamento, deixando 5107 municípios sem acesso ao serviço [2]. Essa carência generalizada e a má distribuição geográfica impactam diretamente na saúde da população, forçando milhares de pacientes a percorrerem longas distâncias para ter acesso ao exame. Em 2017, mais de 39% dos exames foram realizados fora do município de residência do paciente, conforme ilustrado na Figura 1 (a); já a Figura 1 (b) ilustra a gravidade dessa desigualdade ao destacar o fluxo de pacientes em direção ao estado de São Paulo, que concentrou a realização de exames para diferentes regiões do país [2].

(a) Distribution of MRIs in Brazil. (b) Flow for MRI scan in São Paulo.

Figura 1: Distribuição de equipamentos de MRI no Brasil, destacando: (a) desigualdade de acessibilidade dos exames no país e (b) fluxo para exames de MRI em São Paulo [2].

Essa disparidade evidencia uma situação crítica de acessibilidade e iniquidade no

Sistema Único de Saúde (SUS), contribui para o baixo aproveitamento da capacidade instalada nacionalmente, que em 2017 correspondia a apenas 21,45% do total disponível; além disso, o setor privado apresenta maior aquisição de equipamentos e crescimento no número de exames, superando as metas recomendadas pelo Ministério da Saúde, enquanto o sistema público não as atinge, aprofundando a desigualdade no acesso[4].

Nesse contexto, o desenvolvimento de tecnologia nacional na área de RM surge como uma alternativa para reduzir custos e ampliar o acesso a esse tipo de exame. Em 2024, o CNPEM desenvolveu parcialmente um protótipo de MRI de 0,4 T, demonstrando capacidade em produzir equipamentos nesse campo. Entretanto, devido ao curto período do projeto, de apenas um ano, parte do equipamento foi desenvolvida no Centro, com exceção dos sistemas de eletrônica e controle, que foram adquiridos de fornecedores externos. Com o objetivo de desenvolver um equipamento integralmente nacional, torna-se necessário o desenvolvimento do console, responsável pelo controle do sistema de RM. Dentro desse contexto, o presente trabalho tem como foco uma etapa do processo de transmissão do console, a geração de pulsos de RF. Além de ser uma etapa inicial de prova de conceito para o desenvolvimento do equipamento, a experiência adquirida nesse processo é importante para a capacitação da equipe e o aprofundamento do conhecimento técnico. Este projeto serve como uma base de aprendizado, de modo que, no futuro, os desenvolvimentos subsequentes possam ser aprimorados e otimizados, contribuindo para a autonomia tecnológica do país na área de saúde.

## 2 OBJETIVOS

Este capítulo abordará na Seção 2.1, o objetivo geral e, na Seção 2.2 os objetivos específicos do presente trabalho.

### 2.1 Objetivo Geral

Desenvolver e validar um gerador digital de pulsos de RF implementado em FPGA, utilizando a placa de desenvolvimento Red Pitaya e a linguagem de descrição de hardware VHDL para um protótipo de RM, contribuindo para o desenvolvimento de um equipamento com tecnologia nacional.

### 2.2 Objetivos Específicos

- Estudar os princípios físicos e eletrônicos envolvidos na geração de pulsos de RF utilizados em sistemas de RM.

- Analisar os principais tipos de pulsos de RF para equipamentos de RM e técnicas de janelamento (*windowing*).

- Implementar a técnica de Síntese Digital Direta (em inglês, Direct Digital Synthesis DDS) em FPGA, desenvolvendo módulos dedicados à geração de pulsos, à geração de portadoras e à modulação em quadratura, visando a construção de um gerador digital de sinais de RF.

- Validar o funcionamento dos módulos digitais por meio de simulações e *testbenches* desenvolvidos na ferramenta Vivado, comparando os resultados com referências obtidas em ambiente Python.

- Integrar os módulos desenvolvidos e realizar a verificação experimental do sinal transmitido em um osciloscópio, avaliando a coerência entre os resultados simulados e os obtidos na implementação física.

### 3 FUNDAMENTAÇÃO TEÓRICA

Neste capítulo, serão apresentados alguns conceitos teóricos necessários para entender o trabalho desenvolvido. A Seção 3.1 aborda os princípios físicos da técnica de RM.

A Seção 3.2 apresenta o console, equipamento que controla o sistema de RM, discutindo suas funções de sincronização, transmissão e recepção de sinais. Por fim, a Seção 3.3 trata do processamento digital de sinais de RF, abordando a modulação IQ (Seção 3.3.1) e a geração de pulsos de RF utilizando a técnica de DDS (Seção 3.3.2).

#### 3.1 Ressonância Magnética Nuclear (RMN)

Nesta seção, são apresentados os conceitos fundamentais de RMN, detalhando o fenômeno de na Seção 3.1.1 e os componentes de um equipamento de RM na Seção 3.1.2. Em seguida, são descritos os principais tipos de pulsos de RF utilizados em RM (Seção 3.1.3).

##### 3.1.1 Fenômeno de RMN

O fenômeno de RMN consiste na interação de um campo magnético estático intenso com os núcleos atômicos da amostra que possuem momento angular e momento magnético não-nulos. Sob uma perspectiva clássica, núcleos como o do hidrogênio, ao serem submetidos a esse campo, exibem um movimento de precessão, análogo a um pião sob a ação do campo gravitacional. Esse fenômeno ocorre graças a uma propriedade intrínseca de partículas subatômicas conhecida como *spin*. Para que um núcleo possa ser utilizado em RMN, ele deve possuir um *spin* nuclear resultante não-nulo, característica comum em núcleos com número de massa ímpar, como o hidrogênio, principal alvo em IRM devido à sua abundância no corpo e alta sensibilidade à técnica [1, 3].

Quando submetidos a um campo magnético externo, o momento magnético associado ao spin de cada próton se orienta em relação ao campo. Sob o tratamento da mecânica quântica, o próton pode se orientar em duas orientações em relação ao campo externo, paralelo ao  $B_0$  (*spin-up*), que corresponde ao estado de menor energia, ou antiparalelo (*spin-down*), que representa o estado de maior energia. A equação que relaciona a frequência de oscilação (denominada de frequência de Larmor) e a intensidade do campo magnético é descrita na Equação 1 [1, 5, 5].

$$\omega = \gamma B_0 \quad (1)$$

Onde  $\gamma$  é a razão giromagnética que, no caso do hidrogênio é de 42,58 MHz/T, e  $B_0$  é o campo externo ao qual os spins estão submetidos. A soma vetorial dos momentos magnéticos dos spins submetidos a  $B_0$  forma um vetor de magnetização líquida ( $M$ ), que, no estado de equilíbrio, possui apenas a componente longitudinal, orientada na mesma direção do campo. Para realizar um experimento de RMN, é necessário perturbar o estado de equilíbrio da magnetização, de forma que o vetor  $M$  esteja no plano transversal. Essa reorientação do vetor magnetização acontece com a aplicação de um pulso de RF ( $B_1$ ), perpendicular a  $B_0$  e emitido na frequência de Larmor, fenômeno conhecido como ressonância. Quando esse pulso é aplicado, os spins absorvem energia e o vetor magnetização desloca, formando um ângulo em relação a  $B_0$  [1, 6].

Para que uma corrente elétrica seja induzida na bobina de recepção, posicionada perpendicularmente ao plano transversal, é necessário que o vetor de magnetização, total ou parcialmente, esteja nesse plano e que os spins apresentem coerência de fase. Quando todos os momentos magnéticos individuais são desviados em 90º para o plano transversal e precessam na mesma fase, obtém-se o sinal máximo induzido na bobina [1].

Quando a aplicação do pulso de RF é cessada, o sistema retorna ao seu estado de equilíbrio através dos processos de relaxação da magnetização, gerando um sinal com formato de uma onda senoidal amortecida conhecido como FID [1]. O processo está ilustrado na Figura 2.

Figura 2: Representação do fenômeno de ressonância magnética envolvendo pulso de RF para gerar a magnetização transversal e a geração do FID durante a relaxação [6].

O sinal de RM (FID) detectado pela bobina de recepção do equipamento é digitalizado e processado para formar a imagem, permitindo a visualização detalhada das estruturas anatômicas e funcionais da área em estudo [6]. A codificação espacial da informação é realizada pela aplicação de gradientes de campo magnético, que alteram sutilmente o campo magnético em diferentes posições. Isso faz com que a frequência de Larmor varie espacialmente, permitindo localizar a origem do sinal. Os dados adquiridos

são organizados em uma matriz de frequências espaciais denominada espaço-k (*k-space*). [6, 7]. Após o preenchimento completo do *k-space*, aplica-se a Transformada de Fourier, que converte os dados do domínio da frequência para o domínio espacial, resultando na imagem final [7].

A relaxação dos spins, responsável pelo FID, ocorre devido às trocas de energia entre os próprios spins e entre os spins e o ambiente ao seu redor (rede). Duas constantes de tempo são utilizadas para caracterizar esses processos:  $T_1$  e  $T_2$ . A constante  $T_1$ , ou tempo de relaxação longitudinal, representa o tempo de retorno da magnetização longitudinal para seu estado de equilíbrio, enquanto a constante  $T_2$ , ou tempo de relaxação transversal, descreve o decaimento da magnetização criada no plano transversal. As diferenças intrínsecas nos tempos de relaxação entre os tecidos biológicos são a principal fonte de contraste nas imagens de RM [1]. Esse contraste pode ser acentuado e manipulado pelo uso de sequências de pulsos, que são combinações precisamente temporizadas de pulsos de RF e gradientes de campo magnético, permitindo gerar imagens ponderadas para realçar características teciduais específicas [5].

### 3.1.2 Componentes de um equipamento de MRI

Um equipamento de MRI consiste em um sistema tecnológico complexo, constituído por quatro subsistemas principais que funcionam de forma integrada e sincronizada, sendo eles [7]:

- **Magneto:** É o principal componente do sistema de RM, responsável por produzir o campo magnético estático, intenso e homogêneo, que alinha os momentos magnéticos dos prótons de hidrogênio nos tecidos do corpo. Os tipos de magnetos mais comuns em sistemas de RM são os supercondutores, permanentes e resistivos [7].

- **Sistema de RF:** Este sistema é composto por bobinas de RF responsáveis pela transmissão dos pulsos de excitação e pela recepção dos sinais de RM emitidos pelo corpo. Além disso, o sistema inclui amplificadores de RF, que têm a função de amplificar os pulsos gerados no console e os sinais emitidos pela amostra [6].

- **Sistema de Gradiente:** É responsável pela codificação espacial, que permite localizar os sinais de RM para a formação da imagem [7]. Esse sistema é composto por bobinas de gradiente que geram uma variação linear na intensidade do campo magnético estático ao longo dos três eixos espaciais (x, y e z), e amplificadores de gradiente, responsáveis pela amplificação dos pulsos de gradiente gerados no espectrômetro [6, 8].

- **Console:** Atua como o sistema de controle e processamento do equipamento. É responsável por processar as sequências de pulso, gerando as formas de onda para os sistemas de RF e de gradiente de maneira síncrona. Além disso, realiza a aquisição e a digitalização dos sinais de RM e, posteriormente, a reconstrução da imagem a partir dos dados brutos. O console também serve como uma interface de operação entre o usuário e o equipamento [9]. Esse componente e seus detalhes serão aprofundados na Seção 3.2

Os subsistemas listados estão representados na Figura 3:

Figura 3: Subsistemas de um equipamento de MRI tradicional com magneto do tipo superconductor, que requer escudo térmico e câmara de vácuo para operação[6].

### 3.1.3 Pulsos de Radiofrequência em RM

Como descrito na Seção 3.1.1, em um sistema de RM, os pulsos de RF são fundamentais para excitar os núcleos de hidrogênio, que ao relaxarem, emitem sinais electromagnéticos que são captados pelas bobinas e utilizados para a formação das imagens. O transmissor gera pulsos de RF com parâmetros controlados, como frequência central, largura de banda, amplitude e fase, que determinam a excitação dos núcleos dentro da região desejada [7, 10].

A geração de um pulso de RF envolve a modulação, isto é, a multiplicação de uma onda portadora senoidal por uma envoltória de RF. A frequência da portadora é ajustada para a *frequência de Larmor*, podendo incluir um pequeno deslocamento ( $\Delta f$ ) necessário para a localização da fatia. A envoltória, por outro lado, é uma função que varia mais lentamente no tempo e define a forma do pulso. [8]

A duração do pulso ( $T$ ) geralmente é medida em milissegundos ou segundos. Outro parâmetro importante é a largura de banda, especificada em hertz ou quilohertz, que está relacionada ao conteúdo em frequência do pulso. Além disso, os pulsos de RF podem ser descritos por seu *flip angle* ( $\theta$ ), que representa o ângulo de desvio produzido pela aplicação do pulso. Por exemplo, um pulso de excitação que transfere completamente a

magnetização longitudinal para o plano transversal tem um *flip angle* de  $90^\circ$  ( $\pi/2$  rad). Esse ângulo pode ser calculado por meio da área sob a curva da envoltória do pulso [8].

Estes pulsos são gerados digitalmente, enviados a um DAC, onde são convertidos em sinais analógicos, e posteriormente amplificados para atingir a intensidade necessária para excitar os spins [7], o processo de geração dos sinais digitais será mais aprofundado na Seção 3.3.

Existem várias formas de pulsos de RF, alguns dos formatos mais comumente usados são descritos a seguir:

- **Pulsos Retângulares (“*Hard pulses*”):** possuem a forma de uma função *RECT* no domínio do tempo (Figura 4). Eles são caracterizados por possuirem uma duração temporal curta e amplitude constante. Os *hard pulses* são utilizados quando não há necessidade de seleção espectral ou espacial, uma vez que sua largura de banda é suficientemente ampla para afetar spins com uma grande variedade de frequências de ressonância. Os pulsos retangulares são aplicados sem a presença de um gradiente simultâneo [8].

Figura 4: Forma de onda de um pulso retangular (função *RECT*) no domínio do tempo [8].

A banda de frequências de um pulso *hard* é ampla, e sua forma no domínio da frequência é uma função *sinc* ( $\sin(x)/x$ ), que é a Transformada de Fourier de uma função retangular. O *flip angle* de um *hard pulse* é determinado por [8]:

$$\theta = \gamma B_1 T \quad (2)$$

A implementação de pulsos retangulares pode ser desafiadora devido às descontinuidades na sua forma de onda, o que pode comprometer a reprodução com fidelidade por alguns amplificadores de RF. Nesses casos, uma opção é utilizar um pulso retangular com janelamento, que geralmente funciona melhor. Uma outra alternativa é a utilização de um pulso com forma de onda trapezoidal. Para que um pulso *hard* seja eficaz, ele deve ter uma duração suficientemente curta para garantir que sua largura de banda cubra todas as frequências de interesse no volume de imagem. Por exemplo, durações entre 100 e 500  $\mu$ s resultam em larguras de banda de 2 a 10 kHz, que são ideais para a maioria das aplicações na ausência de gradientes [8].

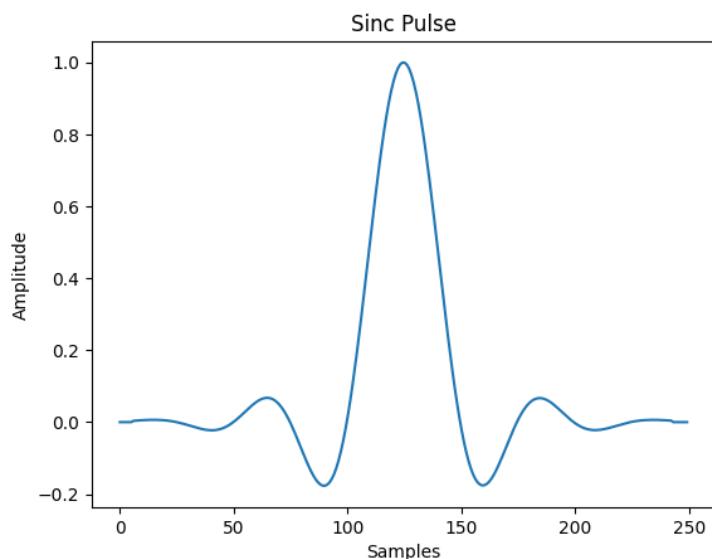

- **Pulsos *sinc*:** amplamente utilizados para excitação seletiva, saturação e refocalização em RM, sendo uma das formas mais comuns de pulsos de RF por produzir perfis de fatia próximos do ideal [8]. A forma de onda de um pulso *sinc* consiste em vários lóbulos adjacentes de polaridade alternada. O lóbulo central apresenta a maior amplitude e é duas vezes mais largo que os lóbulos laterais, cujas amplitudes decaem progressivamente à medida que se afastam do centro [8]. A Figura 5 ilustra o formato de um pulso *sinc*.

Figura 5: Forma de onda de um pulso *sinc* no domínio do tempo.

A Transformada de Fourier de um pulso *sinc* (função  $\text{sinc}(x) = \sin(x)/x$ ) infinito no domínio do tempo é uma função *RECT* que, quando aplicada na presença de um gradiente de seleção de fatia, resulta em um perfil de fatia uniforme. No entanto, para que o pulso possa ser gerado, sua duração deve ser finita, sendo obtida pela truncagem dos lóbulos laterais, mantendo apenas o lóbulo central e alguns de seus vizinhos. Essa truncagem introduz ondulações (ripples) no perfil de excitação, principalmente nas bordas da fatia [8, 7]. Quanto maior o número de lóbulos incluídos, melhor a aproximação ao perfil ideal de frequência, mas isso aumenta a duração do pulso, o que pode prolongar os tempos mínimos de eco (TE) e de repetição (TR) da sequência de pulsos [8].

Para atenuar os efeitos causados pelo truncamento e suavizar o perfil da fatia, geralmente é aplicada uma janela de apodização ao pulso *sinc*, isso consiste em multiplicar o pulso por uma função suavemente variável, como Hanning ou uma Gaussiana, tendo como resultado um perfil de excitação com muito menos ondulações. [8, 7].

- **Pulsos Shinnar-Le Roux (SLR):** desenvolvidos para resolver de forma direta e eficiente o problema inverso do design de pulsos seletivos. Esse problema consiste em determinar qual pulso de RF deve ser aplicado para se obter um perfil de fatia

desejado, a partir das condições iniciais da magnetização. Para pulsos com *flip angles* pequenos, a forma de um pulso de excitação pode ser aproximada pela Transformada Inversa de Fourier do perfil da fatia. No entanto, essa aproximação falha para *flip angles* maiores (entre 30° e 90°), devido à não linearidade das equações de Bloch, exigindo métodos mais avançados para o design preciso desses pulsos [8].

O algoritmo SLR permite calcular o pulso de RF de forma direta, sem a necessidade de processos iterativos. Ele utiliza parâmetros como a largura de banda de RF, duração do pulso, *flip angle*, percentual de *ripple* na banda passante e na banda de rejeição, e o algoritmo retorna o pulso de RF ideal por meio de um processo computacional direto. Essa abordagem também permite ao projetista realizar ajustes entre os parâmetros antes mesmo de gerar o pulso [8].

### 3.2 Console de Controle

Um console de controle, também conhecido como espetrômetro, é um componente eletrônico fundamental dos sistemas de RM, sendo responsável pela transmissão dos pulsos de RF, controle das sequências de pulsos de RF e gradiente de forma sincronizada e pela aquisição e digitalização dos sinais de RM para que possam ser processados para a reconstrução da imagem. O console atua como o “cérebro” do sistema, controlando a aquisição, gerenciando o tempo de eventos e enviando comandos para os componentes de hardware. Além disso, como já mencionado, ele pode atuar como a interface entre o operador e o equipamento. No entanto, o conhecimento detalhado sobre esse componente em grande parte permanece inacessível por conta da natureza proprietária dos sistemas comerciais. Nesse contexto, uma série de trabalhos de código aberto (*open-source*) surgiram como uma alternativa a esses sistemas fechados, buscando fornecer plataformas mais flexíveis, com componentes de baixo custo e facilmente programáveis. Esses projetos, como o Open-source Console for Real-time Acquisition (OCRA) e o “MAgnetic Resonance COnrol System (MaRCoS)”, buscam romper com as limitações de hardware e software, facilitando o desenvolvimento e a pesquisa na área de RM [10, 9, 11].

O funcionamento do console pode ser dividido em duas funções principais: transmissão de pulsos de RF e a aquisição e processamento de sinais de RM. A maioria dos consoles utiliza a tecnologia de Síntese Digital Direta (DDS) para a geração das formas de onda de RF digitais, um tópico que será abordado com mais detalhes na Seção 3.3. Para a realização das tarefas do console, é essencial uma alta coerência de fase entre os diversos pulsos, o que impõe fortes restrições ao controle de tempo. Devido a essa necessidade de precisão e sincronização, placas com FPGA embarcada são frequentemente utilizados como o núcleo dos consoles de RM, sendo adequados para tarefas rápidas e sincronizadas no tempo [10, 9].

Após a geração dos sinais de banda base e de portadora utilizando a tecnologia DDS, esses sinais são modulados por um modulador de forma de onda. Esse processo alinha a frequência da portadora com a frequência de ressonância dos núcleos de hidrogênio, convertendo o sinal de banda base em um sinal de RF. O sinal modulado passa por um DAC e é transformado em um pulso de RF analógico desejado. Os pulsos são intensificados

por amplificadores de potência antes de serem enviados para a sonda [10, 6].

Simultaneamente, o console também gerencia os pulsos de gradiente. As formas de onda de gradiente, geradas digitalmente, são enviadas para um Gradient Power Amplifier (GPA), que as amplifica. Essas formas de onda amplificadas e filtradas acionam as bobinas de gradiente, que são essenciais para codificar espacialmente a imagem. Após a excitação dos núcleos de hidrogênio, o console gerencia a recepção e o processamento dos sinais emitidos pela amostra. O FID é captado pela bobina receptora e passa por um pré-amplificador antes da digitalização pelo Analog-to-Digital Converter (ADC) [12, 10].

Após a digitalização do sinal de RM pelo ADC, inicia-se o processo de recepção digital, no qual o sinal FID precisa passar por um fluxo de processamento que inclui *downconversion* digital e decimação. A etapa de *downconversion* tem como objetivo demodular o sinal de RM. O processo é realizado fazendo a multiplicação do sinal do ADC pelas saídas I e Q de um oscilador em quadratura que opera na frequência de Larmor. Esse processo permite extrair o sinal em banda base. Em seguida, aplicam-se filtros para os processos de decimação e filtragem, utilizados para reduzir a alta taxa de dados dos sinais, com o intuito de melhorar o processamento subsequente [10].

Os dados de RM são temporariamente armazenados e depois transmitidos via Ethernet para um PC. No PC, os dados do espaço-k são submetidos a uma Transformada inversa de Fourier para reconstruir a imagem final que é exibida para o operador [10, 3]. A Figura 6 apresenta o diagrama de blocos de um console de controle em RM, destacando o fluxo de dados no processo de transmissão dos pulsos de RF e gradiente, além do fluxo de recepção e digitalização dos sinais até a reconstrução e visualização da imagem.

Figura 6: Diagrama de blocos de um console de controle em ressonância magnética, ilustrando os fluxos de transmissão e recepção dos sinais.

### 3.3 Processamento Digital de Sinais de RF

Nesta seção, são apresentados os princípios de processamento digital envolvidos na geração de sinais de RF utilizados em sistemas de RM. A Seção 3.3.1 introduz o conceito de modulação em quadratura (*IQ*). Em seguida, são descritos os métodos de geração digital de sinais, com ênfase na técnica de Síntese Digital Direta (DDS) e na arquitetura do Oscilador Controlado Numericamente (NCO), discutidos na Seção 3.3.2.

#### 3.3.1 Modulação *IQ*

A modulação em quadratura (*IQ* – *In-phase/Quadrature*) é um conceito utilizado em sistemas de processamento digital de sinais de RF, baseando-se na decomposição de sinais senoidais em duas componentes ortogonais, denominadas em fase (I) e em quadratura (Q). A terminologia “*IQ*” tem como origem a representação de um sinal de RF que pode ter sua representação por coordenadas polares (representação de amplitude/fase) ou em coordenadas cartesianas. Qualquer sinal senoidal de RF pode ser modelado como um fasor, um vetor girante com amplitude  $A$ , frequência  $\omega$  e fase inicial  $\phi_0$  [13]:

$$y(t) = A \cdot \sin(\omega t + \phi_0) \quad (3)$$

Usando funções trigonométricas, o sinal pode ser decomposto em suas componentes seno e cosseno:

$$y(t) = I \cdot \cos(\omega t) + Q \cdot \sin(\omega t) \quad (4)$$

Onde a amplitude da componente cosseno é definida como a componente em fase ( $I$ ), e a amplitude da componente seno é chamada de componente em quadratura ( $Q$ ) [13].

#### 3.3.2 Geração de Pulses de RF

Atualmente, a maioria dos sistemas de RM emprega tecnologia de Síntese Digital Direta (DDS) para geração de pulsos de RF. Em comparação com métodos analógicos tradicionais de geração de frequência, o DDS oferece vantagens significativas, como a alta resolução de frequência, precisão de fase e rápida comutação de frequência. A arquitetura do DDS é comumente implementada em FPGAs devido à sua aplicação em circuitos de processamento de sinais de alta velocidade, que incluem tabelas de busca e registradores [10].

A técnica de DDS é usada para a geração de formas de ondas analógicas de alta frequência. A arquitetura se baseia em um Oscilador Controlado Numericamente (NCO) e um DAC conforme ilustrado na Figura 7 [13].

Figura 7: Diagrama de um DDS contendo um NCO (linha tracejada) e DAC [13].

Na revisão da literatura foi observado uma variação no uso dos conceitos de DDS e NCO. Alguns trabalhos tratam o NCO como o bloco responsável pela geração digital da portadora, enquanto a técnica de DDS se baseia nos mesmos blocos utilizados no NCO, mas é expandida por meio de um DAC para gerar as formas de onda analógicas [13]. Em outros trabalhos, o processo completo de geração digital de sinais é tratado inteiramente como DDS, sem destacar o NCO como um componente [10]. A utilização dos termos pode variar de acordo com o contexto e o trabalho, embora ambas as abordagens descrevam praticamente a mesma teoria de geração digital de sinais. Nesse trabalho, vamos adotar a ideia de que o NCO se refere especificamente à geração digital da portadora, enquanto o DDS será considerado o sistema completo, englobando o NCO e o DAC para a geração dos sinais analógicos.

O NCO é implementado como um oscilador digital em quadratura, gerando uma sequência de amostras de seno e cosseno. A funcionalidade básica de um NCO consiste em um acumulador de fase (*Phase accumulator*) e um módulo de conversão de fase para amplitude (*Phase to amplitude conversion*) conforme ilustrado na Figura 8 [13].

Figura 8: Diagrama de um NCO com os módulos *phase accumulator* e *phase to amplitude conversion* [13].

O processo inicia com um incremento de fase programável que é fornecido como entrada. A cada ciclo de clock, o incremento de fase (*tuning\_word M*) é adicionada ao *phase accumulator*, que gera um endereço de fase correspondente. A fase total resultante é convertida para o valor de amplitude correspondente, usando uma tabela de consulta (*lookup table*, LUT) onde uma onda senoidal está armazenada. A produção sequencial desses valores constrói a forma de onda digital, que depois é convertida em uma forma de

onda analógica por um DAC. A frequência de saída da forma de onda ( $f_{out}$ ) é determinada pela frequência de clock ( $f_{clk}$ ), pelo *tuning word*  $M$  e pela largura de bits do *phase accumulator* ( $N$ ), a relação é dada pela Equação 5 [13, 10].

$$f_{out} = \frac{M \cdot f_{CLK}}{2^N} \quad (5)$$

O *tuning word* é programável, o que permite a seleção de praticamente qualquer frequência de saída até metade da frequência de clock (frequência de *Nyquist*) e a alteração da frequência ocorre imediatamente após o carregamento de um novo incremento de fase no registrador de sintonia  $M$ . A *lookup table* com as amostras do seno pode conter uma onda senoidal completa ou apenas um quarto de período. Esta otimização é suficiente para a reconstrução da onda senoidal devido a propriedade de simetria da função e reduz a quantidade de espaço de memória necessário (entretanto, os cálculos adicionais necessários para obter a amplitude correta devem ser ponderados em relação à economia de espaço de memória)[13, 14].

Na FPGA, a forma de onda em banda base, como por exemplo, um pulso do tipo *sinc*, pode ser combinada com uma portadora, possibilitando modulação em amplitude e fase, resultando na geração do pulso de RF, esse processo pode ser descrito como uma etapa de *up-conversion*. O termo *up-conversion* refere-se ao processo de conversão de um sinal digital em banda base para um sinal em banda passante, isto é, a transposição da envoltória do pulso para a frequência de operação necessária para excitar a amostra. Essa conversão é realizada pela combinação da portadora, na frequência de interesse, com a envoltória modulante, que controla a amplitude da portadora. O resultado é um sinal de RF centrado na frequência desejada, mas preservando o formato temporal do pulso original. A representação da envoltória em banda base é feita através das componentes em fase (I) e em quadratura (Q), que permitem a modulação IQ, técnica que possibilita o controle independente de amplitude e fase do sinal resultante [10, 13, 11].

## 4 METODOLOGIA

Este capítulo descreve a metodologia adotada para o desenvolvimento do gerador digital de pulsos de RF proposto neste trabalho.

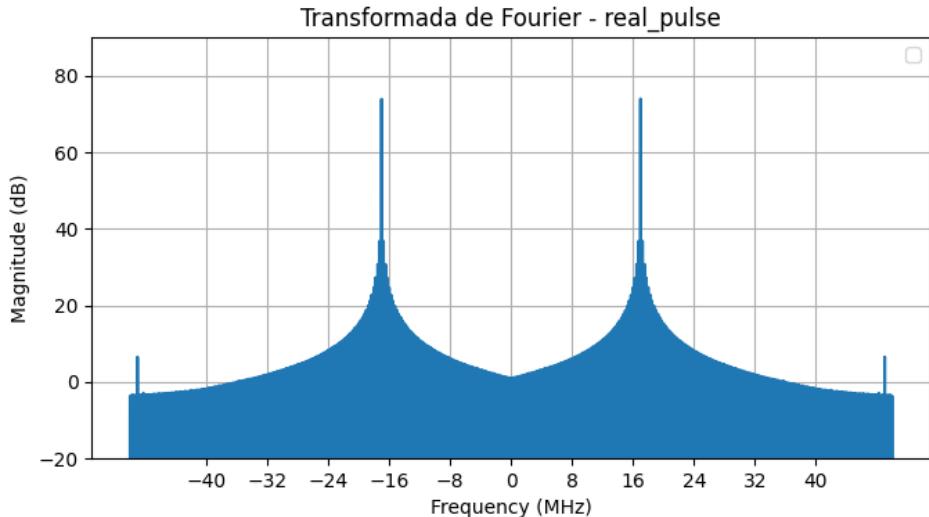

A Seção 4.1 apresenta os requisitos e especificações do sistema. As Seções 4.2 e 4.3 apresentam a geração das amostras em Python utilizadas nos módulos em VHDL. A Seção 4.4 detalha a simulação do comportamento do NCO em Python. Em seguida, a Seção 4.5 apresenta a implementação em VHDL, destacando os módulos de integração. A Seção 4.6 descreve as funcionalidades dos módulos básicos e reutilizáveis. A Seção 4.7 discute o processo de validação dos módulos por meio de *testbenches* e simulações no Vivado. Por fim, a Seção 4.8 mostra os testes em bancada realizados com a FPGA.

## 4.1 Requisitos e Especificações do Sistema

O protótipo de equipamento de MRI desenvolvido pelo CNPEM se baseia em um magneto central, responsável pela geração do campo magnético principal ( $B_0$ ), construído com dois conjuntos de ímãs permanentes. Esses ímãs fornecem um campo de 0,4 T em sua região central. De acordo com a Equação 1 a frequência de Larmor para excitar os spins nesse campo deve ser aproximadamente 17 MHz. Para a operação, o projeto utiliza uma bobina solenoide que atua tanto na transmissão quanto na recepção dos sinais de RF.

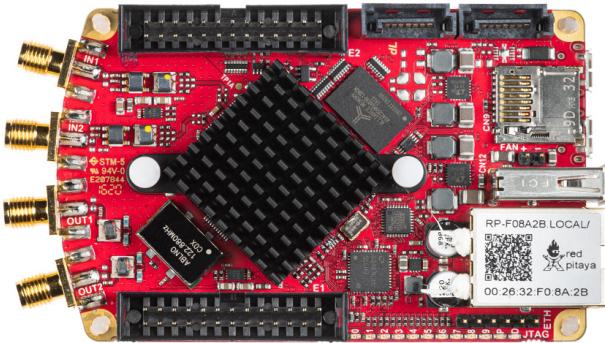

Para atender aos requisitos de geração e aquisição de sinais nessa frequência, optou-se pela utilização da placa comercial Red Pitaya SDRLab 122-16 (Figura 9), empregada em projetos open-source como o OCRA e o MaRCoS [11, 9]. A Red Pitaya é baseada em um *System-on-Chip* (SoC) que integra um processador Dual-Core ARM Cortex-A9 e uma FPGA Xilinx Zynq 7020, com 512 MB de memória RAM DDR3, permitindo o processamento de sinais em tempo real.

Seus recursos de Entrada/Saída (*Input/Output*) incluem dois canais de entrada analógica com ADCs de 16 bits e dois canais de saída com DACs de 14 bits, ambos operando a uma taxa de amostragem de 122,88 MS/s. As entradas e saídas de RF possuem impedância de  $50\ \Omega$  e largura de banda de operação que varia de 300 kHz a 550 MHz para as entradas e até 60 MHz para saídas. Essas características tornam a placa adequada para equipamentos de MRI com campos de até 1,17 T [9], cobrindo com margem a frequência de interesse deste trabalho de 17 MHz.

Figura 9: Placa comercial Red Pitaya 122-16.

## 4.2 Geração de Pulses de RF em Python e Conversão para Ponto Fixo

Nesta etapa, foram gerados diferentes formatos de pulsos de RF em ambiente *Python*, com o objetivo de gerar a envoltória com as amostras dos formatos de pulsos para a implementação em VHDL. Foram explorados diferentes formatos de pulsos e janelas de apodização, variando parâmetros e realizando a análise espectral para observar a resposta

em frequência do pulso. Essa resposta determina, mediante a aplicação simultânea de um gradiente de seleção de fatia, a espessura e a forma da fatia a ser imageada.

A geração dos pulsos foi realizada por meio de uma classe desenvolvida em Python para este trabalho, que permite configurar parâmetros como o tipo de pulso, amplitude, taxa de amostragem, duração, e tipo de janela de apodização. Foram implementadas janelas do tipo Hamming, Hanning e Gaussiana, de modo a permitir o estudo comparativo de diferentes perfis de suavização. Após a geração, cada forma de onda foi analisada tanto no domínio do tempo quanto no domínio da frequência. Neste contexto, utilizamos a Transformada Discreta de Fourier (DFT) (implementada via FFT) para obter o espectro de magnitude dos sinais, expresso em dB relativos, o que é suficiente para a determinação da largura de banda dos pulsos.

Para a validação do fluxo de processamento, optou-se pela utilização de um caso representativo, um pulso *sinc* janelado com Hamming, ilustrado na Figura 10. O pulso *sinc* foi gerado com uma duração de  $300 \mu\text{s}$  e 5 cruzamentos por zero (*zero-crossings*), utilizando uma taxa de amostragem (*sample rate*) de aproximadamente 833,33 kHz (definida pela relação  $50 * (\text{N\_CROSSINGS} / \text{PULSE\_DURATION})$ ), garantindo que o pulso fique bem amostrado. A janela Hamming foi aplicada com comprimento equivalente a 95% da duração total do pulso, totalizando 250 amostras e suavizando as transições nas extremidades do pulso. Depois, as amostras calculadas (pontos) da forma de onda foram convertidas para representação em aritmética de ponto fixo de 14 bits: os 13 bits menos significativos codificam a parte fracionária normalizada ( $0 < \text{valor} \leq 1$ ) do valor e o 1 bit mais significativo restante é usado para codificar o sinal (0=positivo e 1=negativo). As amostras foram passadas para binário e ao final, gerou-se um arquivo txt contendo uma amostra por linha para ser usado na implementação em VHDL.

Figura 10: Pulso *sinc* janelado com Hamming (250 amostras) gerado em Python.

Os parâmetros do pulso foram selecionados de forma a gerar um conjunto de amos-

tras do pulso *sinc* com o objetivo de validar a implementação em VHDL, sem a pretensão de otimizar para uma aplicação específica em MRI. A arquitetura desenvolvida é parametrizável, permitindo que diferentes formatos de pulso possam ser gerados modificando os parâmetros no script Python e gerando um novo arquivo de dados.

Para estabelecer uma referência para a validação temporal e espectral, o pulso de 250 amostras foi interpolado em Python simulando o comportamento do bloco *Pulse\_Gen* (Seção 4.5.2), com o fator de divisão (*division\_factor*) igual a 400 e frequência de clock de 100 MHz. Realizou-se a DFT via FFT para determinar a largura de banda da envoltória em banda base, usando como critério -10 dB em relação ao pico central do espectro. Essa análise estabelece o valor esperado para o sistema, servindo como referência para a validação dos resultados da implementação em VHDL e das medições experimentais. Este pulso interpolado também serviu para uso como vetor de teste para validação do módulo *Pulse\_Gen* posteriormente.

O pulso utilizado neste trabalho serve como estudo de caso para validar o fluxo completo de desenvolvimento, desde a geração do sinal em ambiente de alto nível até sua implementação em hardware. Para aplicações futuras, pulsos com características específicas podem ser integrados ao sistema.

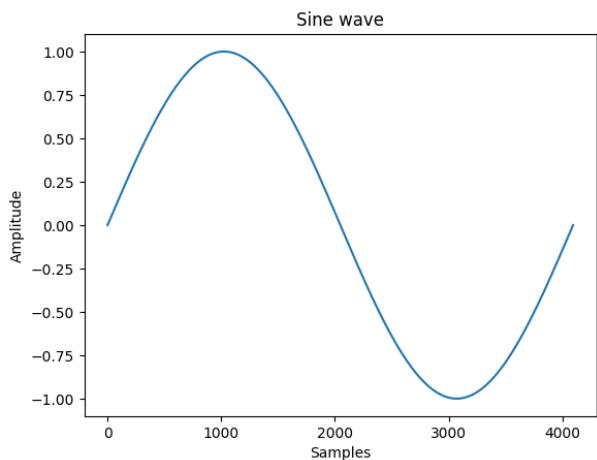

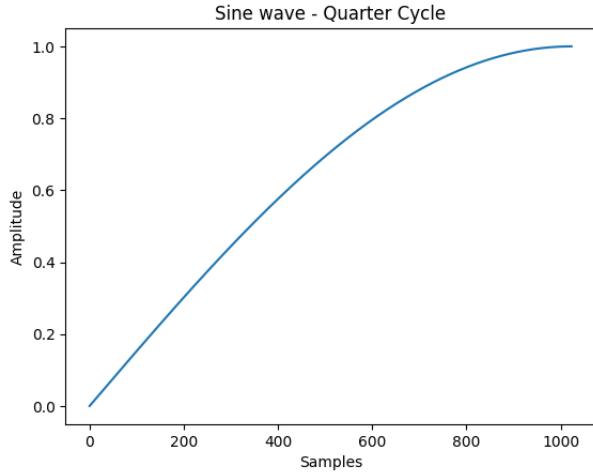

### 4.3 Geração de Um Quarto da Onda Senoidal

Para a geração das amostras armazenadas na ROM, foi desenvolvido um script em Python responsável por criar um quarto do período ( $1/4$ ) de uma onda senoidal, que é posteriormente utilizado pelo módulo *Phase\_To\_Address* em VHDL para reconstruir o período completo da senoide e gerar o cosseno defasado em  $90^\circ$ . Definiu-se o número total de amostras por período com uma resolução de 12 bits (*SAMPLES\_SIZE* = 4096). A geração do sinal senoidal é feita através da função *numpy.sin()*, que calcula os valores de  $\sin(\theta)$  para um vetor de pontos igualmente espaçados entre 0 e  $2\pi$ . A Figura 11 ilustra a onda senoidal gerada com um período com 4096 amostras:

Figura 11: Um período da onda senoidal gerada com 4096 amostras.

Depois, seleciona-se apenas um quarto de período (Figura 12), fazendo `QUARTER_CYCLE = SAMPLES_SIZE/4`, resultando em 1024 amostras que serão armazenadas na ROM.

Figura 12: Um quarto do período da onda senoidal gerada com 1024 amostras.

Por fim, as amostras do um quarto de onda foram convertidas para ponto fixo com 14 bits (13 bits fracionários e 1 bit de sinal) e salvas em um arquivo de texto (.txt), seguindo o mesmo procedimento descrito na Seção 4.2 para o pulso *sinc*.

#### 4.4 Simulação do comportamento do NCO em Python

Para validar o funcionamento do NCO antes de fazer a implementação em VHDL, foi desenvolvida uma simulação em Python que reproduz o seu comportamento. O objetivo foi validar se a frequência das portadoras muda de acordo com o valor de `tuning_word`, e se o seu espectro de magnitude esta centrada na frequência correta. Para fazer esse processo, foi criada uma classe para gerar as amostras das funções seno e cosseno. O número de amostras é determinado pela resolução de bits definida para o acumulador de fase (`bit_resolution`), correspondendo a  $2^N$  pontos igualmente espaçados entre 0 e  $2\pi$ . Essas amostras são usadas na classe `NCO` que faz o mecanismo de incremento e endereçamento de fase. A partir da Equação 5, o incremento de fase (`tuning_word` M) pode ser calculado conforme a Equação 6, em função da frequência desejada ( $f_{out}$ ), da frequência de amostragem ( $f_s$ ) e da resolução do acumulador ( $N$ ):

$$M = \frac{f_{out} \cdot 2^N}{f_{CLK}} \quad (6)$$

A cada passo da simulação, o endereço é atualizado somando o valor do `tuning_word`, e as amostras correspondentes das ondas seno e cosseno são obtidas. Esse processo reproduz o comportamento do acumulador de fase e da geração periódica de portadoras senoidais e cossenoidais.

Para a análise, foram simuladas diferentes frequências de saída (1, 5, 10, 17, 20 e 25 MHz) considerando uma frequência de amostragem de 100MHz e resolução de 12 bits. Em seguida, os sinais foram quantizados em ponto fixo com 14 bits totais e 13 fracionários, reproduzindo o mesmo formato usado na implementação em VHDL.

O comportamento do NCO foi analisado tanto no domínio do tempo, observando as formas de onda senoidal e cossenoidal geradas, quanto no domínio da frequência, por meio do cálculo da DFT para validar se conforme a variação do `tuning_word` gerava a frequência de saída correspondente.

Também foi possível determinar a resolução de frequência do NCO, ou seja, o menor incremento de frequência obtido a cada variação unitária do incremento de fase. Essa resolução é dada por:

$$f_{res} = \frac{f_s}{2^N} \quad (7)$$

Onde  $f_s$  é a frequência de amostragem e  $N$  corresponde ao número de bits do acumulador de fase. Para os parâmetros utilizados na simulação ( $f_s = 100MHz$  e  $N = 12$ ), a resolução de frequência obtida foi de aproximadamente 24,4 kHz. Esse valor representa o “pulo” mínimo de frequência entre duas saídas possíveis do oscilador digital, e está diretamente relacionado ao tamanho do acumulador, ou seja, quanto maior o número de bits, menor será o passo de variação de frequência.

## 4.5 Implementação em VHDL

Esta seção apresenta a implementação em VHDL dos módulos que compõem o gerador digital de pulsos de RF. A Seção 4.5.1 descreve o módulo `IQ_Modulation`, responsável pela modulação do sinal. A Seção 4.5.2 apresenta o módulo `Pulse_Gen`, que realiza a geração da envoltória do pulso. Por fim, a Seção 4.5.3 apresenta o módulo `NCO` responsável por gerar as portadoras utilizadas no sistema.

### 4.5.1 Modulação IQ (`IQ_Modulation`)

O módulo `IQ_Modulation` integra os blocos `Pulse_Gen` e `NCO` para realizar a modulação do pulso de RF. O funcionamento do módulo inicia-se com a geração simultânea da envoltória do pulso *sinc* pelo bloco `Pulse_Gen` e das portadoras senoidal e cossenoidal pelo `NCO`. Nesta implementação, optou-se por gerar o pulso *sinc* somente com a componente real. Dessa forma, a mesma envoltória real gerada pelo `Pulse_Gen` é utilizada como entrada para ambas as componentes I e Q do modulador. Esta abordagem foi adotada propositalmente com o objetivo de simplificar o *hardware* e focar na etapa de controle de frequência via DDS/NCO. Extensões futuras podem explorar perfis complexos com fase arbitrária, como nos pulsos do tipo SLR.

O `Pulse_Gen` é configurado com parâmetros para gerar a envoltória do pulso *sinc* com duração controlada, enquanto o `NCO` é parametrizado para produzir as portadoras senoidal e cossenoidal na frequência de interesse. O bloco `IQ_Modulation` executa as

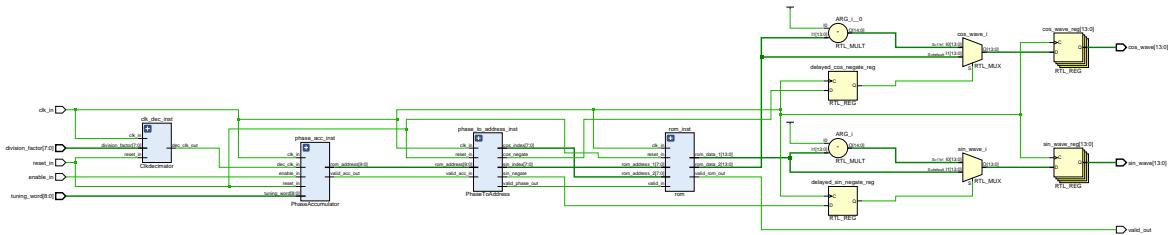

multiplicações entre a envoltória do pulso e cada uma das portadoras, esse processo é sincronizado pelo sinal de validação `valid_in_nco`, proveniente do NCO, este sinal atua como habilitador para o processo da modulação. Os sinais de saída do `IQ_Modulation` são então o `real_pulse` (multiplicação do pulso por cosseno) e `imaginary_pulse` (multiplicação do pulso por seno). O diagrama do módulo está ilustrado na Figura 13

Figura 13: Diagrama do módulo `IQ_Modulation`. O símbolo circular em vermelho representa a operação de multiplicação entre os sinais da envoltória gerada pelo `Pulse_Gen` e as portadoras senoidal e cossenoidal do `NCO`.

#### 4.5.2 Gerador de Pulso (`Pulse_Gen`)

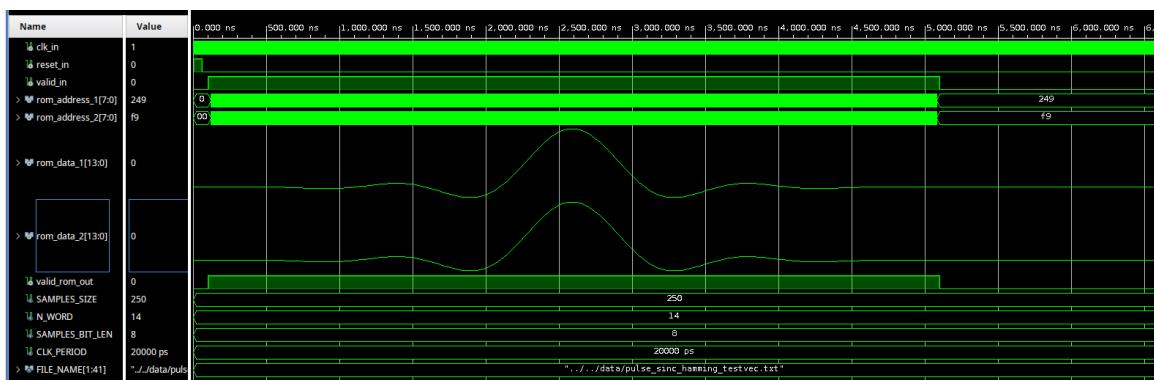

O módulo `Pulse_Gen` tem como função integrar os módulos `Clk_Decimator` (Seção 4.6.1), `Phase_Accumulator` (Seção 4.6.2) e `ROM` (Seção 4.6.4) para a geração do pulso *sinc*. Sua principal função é conectar as portas de entrada e saída desses blocos, além de gerenciar os parâmetros genéricos do sistema, como o número de amostras (`SAMPLES_SIZE`), a largura de bits dos dados (`N_WORD`) e o caminho para o arquivo de amostras (`FILE_NAME`).

O fluxo de dados e controle dentro do `Pulse_Gen` inicia com o `Clk_Decimator`. Este módulo recebe o clock principal (`clk_in`) e um `division_factor` para gerar um clock de pulso mais lento (menor frequência), o `dec_clk_out`. Este sinal determina quando o `Phase_Accumulator` pode fazer o incremento de endereço.

O `Phase_Accumulator` atua como um contador, avançando em cada pulso de `dec_clk_in`. Ele gera endereços sequenciais (`rom_address`) que são usados para acessar as amostras na memória `ROM`. Para a geração do pulso *sinc*, o `tuning_word` foi definido como 1, garantindo que o acumulador avance em um passo por vez e leia todas as amostras em sequência. O `division_factor` foi mantido igual a 400 para gerar um pulso com duração de 1 ms (As definições desses valores são explicadas nas Seções 4.6.1 e 4.6.2). A cada avanço, o `Phase_accumulator` também gera um sinal de validação (`valid_acc_out`), indicando que um novo endereço está disponível.

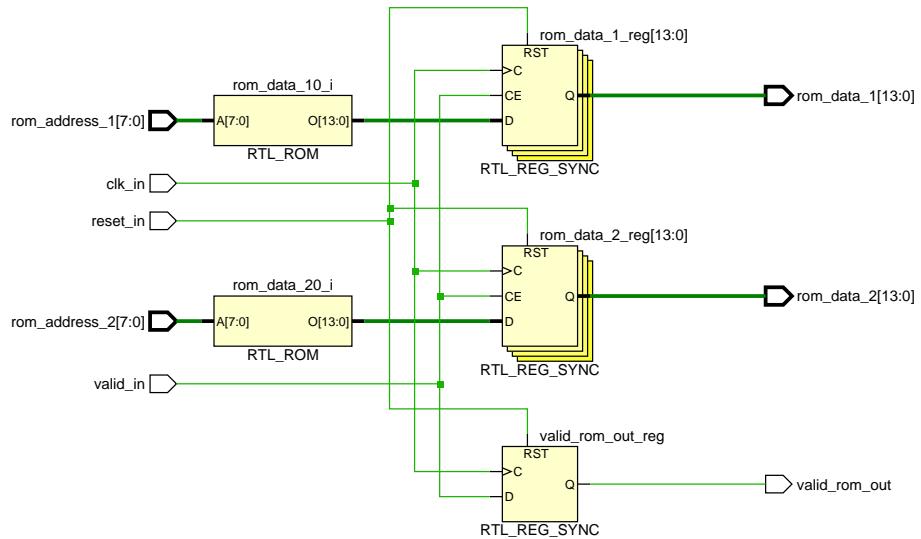

O sinal de saída `valid_acc_out` conecta no `valid_in` da ROM, servindo como um sinal de habilitação. A ROM libera a amostra correspondente (`rom_data_1`) e um sinal de validação (`valid_rom_out`) que confirma a disponibilidade do dado. As saídas finais do módulo `Pulse_Gen` são o pulso `sinc` (`rom_data_out`) e seu sinal de controle (`valid_out`). O diagrama do módulo `Pulse_Gen` está ilustrado na Figura 14.

Figura 14: Diagrama do módulo `Pulse_Gen` com os sinais de entrada e saída.

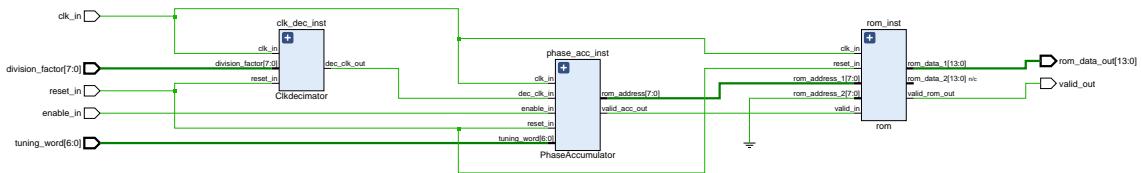

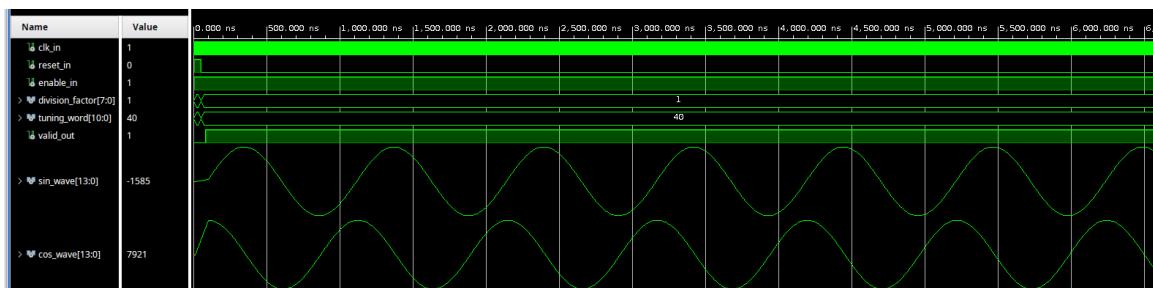

#### 4.5.3 Gerador das Portadoras (NCO)

O módulo `NCO` é responsável pela geração das portadoras senoidal e cossenoidal utilizadas na modulação do pulso de RF. Ele integra quatro módulos, o `Clk_Decimator` (Seção 4.6.1), o `Phase_Accumulator` (Seção 4.6.2), o `Phase_to_Address` (Seção 4.6.3) e a `ROM` (Seção 4.6.4). Sua função é conectar e gerenciar os sinais entre esses blocos, além de definir os parâmetros genéricos do sistema, como a quantidade de amostras e o arquivo `.txt` contendo um quarto de onda do seno.

O fluxo de operação inicia-se no bloco `Clk_Decimator`, que recebe o sinal de clock principal `clk_in` e o `division_factor`, gerando um clock de saída `dec_clk_out`. No contexto desta implementação, o valor de `division_factor` foi mantido igual a 1, de forma a utilizar a frequência máxima disponível do clock da placa. Esse sinal é então utilizado para sincronizar o incremento de fase no `Phase_Accumulator`.

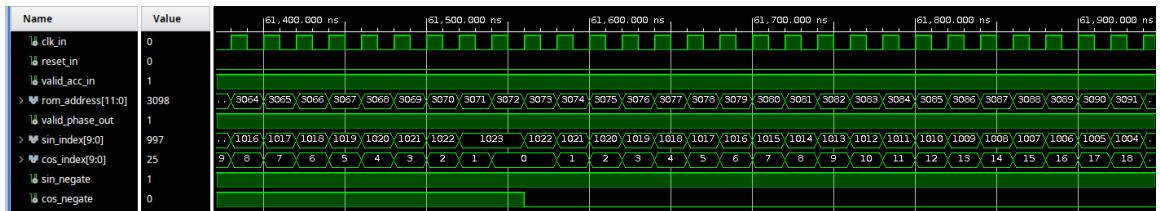

O `Phase_Accumulator` atua como um contador controlado por clock, responsável por gerar os endereços de fase (`Phase_Accumulator`) a partir do valor de incremento (`tuning_word`). Esse parâmetro define a frequência das portadoras geradas. A cada incremento, o módulo também emite o sinal de validação `valid_acc_out`, indicando a disponibilidade de um novo endereço válido.

Em seguida, o módulo `Phase_to_Address` recebe o endereço `rom_address` e o converte em endereços específicos para leitura das amostras `sin_index` e `cos_index`. Esse bloco implementa a lógica necessária para reconstruir o sinal completo das portadoras utilizando apenas um quarto de onda armazenado na `ROM`. Ele também é responsável por gerar os sinais de controle `sin_negate` e `cos_negate`, que determinam quando a saída deve ser invertida para reproduzir corretamente os quatro quadrantes do período senoidal. O sinal `valid_phase_out` é emitido por este bloco para indicar que os endereços e sinais de negação estão prontos e válidos para leitura na `ROM`.

A ROM armazena as amostras do quarto de onda da senoide em formato de ponto fixo de 14 bits (1 bit de sinal e 13 fracionários). O arquivo especificado em `FILE_NAME` contém essas amostras, previamente geradas em Python. Durante a operação, a ROM recebe os endereços `sin_index` e `cos_index` e libera as amostras correspondentes `rom_data_1` e `rom_data_2`, além de gerar o sinal de controle `valid_out`.

Por fim, as amostras lidas da ROM passam pela lógica de negação, implementada por dois processos síncronos. Essa etapa aplica o sinal de inversão (`sin_navigate` ou `cos_navigate`) às respectivas amostras, completando a reconstrução do sinal. O resultado são as saídas `sin_wave` e `cos_wave`, correspondentes às portadoras senoidal e cossenoidal defasadas em 90°.

O diagrama do módulo NCO, apresentado na Figura 15, ilustra a integração entre os blocos e o fluxo de dados e controle descritos.

Figura 15: Diagrama do módulo NCO com os sinais de entrada e saída.

## 4.6 Módulos Básicos e Reutilizáveis

Os módulos foram desenvolvidos de forma que fossem reutilizáveis tanto para a geração do pulso de RF quanto para a geração das portadoras no NCO.

### 4.6.1 Clock Decimator (Clk\_Decimator)

O módulo `Clk_Decimator` tem como objetivo controlar a duração total do pulso de RF, atuando como um divisor de frequência que gera um sinal de habilitação periódico para o módulo `Phase_Accumulator`. Ele funciona como um contador que recebe um sinal de entrada chamado `division_factor`. A cada ciclo do clock da FPGA, o contador é incrementado até atingir o valor definido por `division_factor`. Quando isso ocorre, o sinal de saída (`dec_clk_out`) é ativado por um ciclo de clock, e o contador é reiniciado. O diagrama do módulo com os sinais está representado na Figura 16.

Figura 16: Diagrama do módulo `Clock_Decimator` com os sinais de entrada e saída.

O parâmetro genérico `DIV_RES` define a largura do contador, ou seja, o número de bits utilizados para representar o valor de `division_factor`. Esse parâmetro estabelece o intervalo máximo de contagem, permitindo ajustar a resolução temporal do sinal de saída.