# IMPLEMENTAÇÃO DIGITAL DE REDES NEURAIS ARTIFICIAIS PARA O CONTROLE DE MOTOR DE INDUÇÃO

## ANDRÉ MUNIZ SOARES

CAMPO GRANDE 2006

# UNIVERSIDADE FEDERAL DO MATO GROSSO DO SUL PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

# IMPLEMENTAÇÃO DIGITAL DE REDES NEURAIS ARTIFICIAIS PARA O CONTROLE DE MOTOR DE INDUÇÃO

Dissertação submetida à

Universidade Federal de Mato Grosso do Sul

como parte dos requisitos para

obtenção do grau de Mestre em Engenharia Elétrica.

### ANDRÉ MUNIZ SOARES

Campo Grande, Dezembro de 2006.

# IMPLEMENTAÇÃO DIGITAL DE REDES NEURAIS ARTIFICIAIS PARA O CONTROLE DE MOTOR DE INDUÇÃO

#### André Muniz Soares

'Esta Dissertação foi julgada adequada para obtenção do Título de Mestre em Engenharia Elétrica, Área de Concentração em Energia Elétrica, e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Mato Grosso do Sul - Campo Grande - MS.'

| Ι                   | Luciana Cambraia Leite, Dra.<br>Orientadora     |              |

|---------------------|-------------------------------------------------|--------------|

|                     |                                                 |              |

| Joá                 | ão Onofre Pereira Pinto, Ph.D.<br>Co-orientador |              |

| Coordenador do Prog | grama de Pós-Graduação em Engenha               | ria Elétrica |

|                     | Banca Examinadora:                              |              |

| I                   | Luciana Cambraia Leite, Dra.<br>Presidente      |              |

| Joá                 | ão Onofre Pereira Pinto, Ph.D.                  |              |

| Luiz                | Eduardo Borges da Silva, Ph.D.                  |              |

| Flávio              | Alessandro Serrão Gonçalves, Dr.                |              |

Milton Ernesto Romero, Ph.D.

A Deus que sempre esteve ao meu lado nessa caminhada Aos meus pais e irmãs, pelo amor, dedicação e apoio.

#### **AGRADECIMENTOS**

Aos professores Dra. Luciana Cambraia Leite e Dr. João Onofre Pereira Pinto, minha orientadora e co-orientador, respectivamente, pelo apoio e pelas contribuições que foram fundamentais para o desenvolvimento deste trabalho.

Aos Professores Luiz Eduardo Borges da Silva e Milton Ernesto Romero, pelas valiosas contribuições na etapa de Qualificação desta Dissertação de Mestrado.

Às empresas *Texas Instruments*, *Altera* e *Pi componentes*, por acreditarem em meu trabalho e pelas valiosas doações materiais.

Aos professores e funcionários do mestrado e do departamento de Engenharia Elétrica – DEL – UFMS por seu auxílio.

A equipe de pesquisadores do Batlab (Laboratório de Inteligência Artificial, Eletrônica de Potência e Eletrônica Digital), especialmente aos meus grandes amigos e incentivadores Gilberto S. Tatibana e Márcio L. Portella.

Resumo da Dissertação apresentada a UFMS como parte dos requisitos necessários para a obtenção do grau de Mestre em Engenharia Elétrica.

# IMPLEMENTAÇÃO DIGITAL DE REDES NEURAIS ARTIFICIAIS PARA O CONTROLE DE MOTOR DE INDUÇÃO

#### **André Muniz Soares**

Dezembro/2006

Orientador: Luciana Cambraia Leite, Dra.

Co-orientador: João Onofre Pereira Pinto, Ph.D.

Área de Concentração: Energia Elétrica.

Palavras-chave: acionamento de motores de indução, controle vetorial sensorless,

neurohardware, FPGAs. Número de Páginas: 120.

RESUMO: Este trabalho tem como contribuição a implementação de redes neurais artificiais utilizadas no controlador "sensorless" do motor de indução trifásico. Estas redes neurais foram representadas como circuitos dentro de um FPGA (Field Programmable Gate Array), constituídas por neurônios representados por processadores digitais independentes e sintetizados em VHDL. Para a tarefa de representação da função de ativação sigmoidal dos neurônios em hardware, fez-se uso da técnica de interpolação "spline". Como resultado final do trabalho, foi construído um protótipo do controlador do motor de indução trifásico, composto por um FPGA gerenciado por um DSP (processador digital de sinais), controlando circuitos de potência para seu acionamento. O trabalho inicia-se com ênfase em uma revisão bibliográfica sobre estratégias de controle de motores de indução e implementação em hardware de redes neurais. A seguir, o sistema proposto é apresentado, iniciando pela apresentação de seus blocos constituintes, para finalizar com uma descrição dos circuitos do protótipo completo. Finalmente, são apresentados resultados experimentais de testes com o protótipo e conclusões finais.

Abstract of Dissertation presented to UFMS as a partial fulfillment of the requirements for the degree of Master in Electrical Engineering.

#### A Neural-Network-Digital Implementation for Induction Motor Drive

#### **André Muniz Soares**

#### December / 2006

Advisor: Luciana Cambraia Leite, Dra.

Co-advisor: João Onofre Pereira Pinto, Ph.D. Area of Concentration: Electrical Energy.

Keywords: induction motors drives, sensorless vector control, neurohardware, FPGAs.

Number of Pages: 120.

ABSTRACT: This work describes a neural-network-based implementation used in 'sensorless' space-vector control for induction motor drives. These neural-networks were represented as circuits inside of a FPGA (Field Programmable Gate Array), employed by neurons performed by independent digital processors and synthesized in VHDL. In order to achieve the building of the sigmoidal activation function for digital implementations of neurons, it has been used the "spline" interpolation technique. As results, it was built a hardware system structure to drive an induction motor, which is composed by a FPGA managed by a DSP (digital signal processor), and so to control the power electronics. In the beginning, great emphasis is laid on description of the various strategies of induction motors control, and the neural networks hardware implementations. Next, the proposed system is presented, and it is goal to give a brief description of the built blocks. In addition, it is presented a description of the final prototype circuits. Then, the experimental parts are presented to demonstrate the performance of tests with the prototype and the work closes with conclusions.

# **SUMÁRIO**

| CAPÍTU     | JLO 1 - INTRODUÇÃO                                             | 1        |

|------------|----------------------------------------------------------------|----------|

| 1.1        | Introdução                                                     | 1        |

| 1.2        | O motor de indução e o acionamento em velocidades variáveis    | 1        |

| 1.3        | O controle da máquina de indução: escalar e vetorial           | 2        |

| 1.4        | Técnicas de controle inteligente                               | 3        |

| 1.5        | Implementação de redes neurais artificiais (RNA) em hardware   |          |

| 1.6        | Descrição dos capítulos                                        |          |

| 1.7        | Considerações finais                                           |          |

|            | JLO 2 - CONTROLE DE MOTOR DE INDUÇÃO COM ORIENTAÇÃO            | DO       |

|            | ) ESTATÓRICO                                                   |          |

| 2.1        | Introdução                                                     |          |

| 2.2        | Visão geral do sistema                                         |          |

| 2.3        | Subsistema de circuito de potência.                            |          |

| 2.3        | <u>*</u>                                                       |          |

| 2.3        | ,                                                              |          |

| 2.4        | Subsistema de Processamento de Sinais.                         |          |

| 2.4        |                                                                |          |

| 2.4        |                                                                |          |

| 2.4        |                                                                |          |

| 2.4        |                                                                |          |

| 2.5        | Considerações finais                                           |          |

|            | JLO 3 - ESTRUTURA INTERNA DOS BLOCOS "CONTROLE PWM             | 21       |

|            | -VECTOR BASEADO EM REDES NEURAIS" E "ESTIMADOR DE              |          |

| FLUXC      |                                                                | 22       |

| 3.1        | Introdução                                                     | 22       |

| 3.1        | Estrutura do bloco "Controle PWM Space-Vector Baseado em Redes | 44       |

|            | ais"                                                           | 22       |

| 3.3        | Estrutura do bloco "Estimador de Fluxo"                        |          |

| 3.3<br>3.4 | Considerações finais                                           |          |

|            | JLO 4 - DESCRIÇÃO DO HARDWARE DO SISTEMA PROPOSTO              | ∠o<br>20 |

| 4.1        |                                                                |          |

| 4.1        | Introdução                                                     |          |

|            |                                                                |          |

| 4.3        | Subsistema Analógico (medição e condicionamento de sinais)     |          |

| 4.4        | Conversão analógica para digital (ADS8364)                     |          |

| 4.5        | Hardware do bloco Estimador de Fluxo                           |          |

| 4.5        |                                                                |          |

|            | .2 Transformação Trifásica e Rede Recorrente Híbrida com MLP   |          |

|            | 4.5.2.1 Controlador de Camada de Rede Neural                   |          |

|            | 4.5.2.2 Neurônio digital com função de ativação linear         | 42       |

|            | 4.5.2.3 Neurônio digital com função de ativação sigmóide       |          |

| 4.6        | Hardware do bloco Estimador de Sinais                          |          |

| 4.6        | $\boldsymbol{\mathcal{E}}$                                     |          |

| 4.7        | Hardware do bloco "Controlador"                                |          |

| 4.7        | <del> </del>                                                   | 56       |

| 4.8        | Hardware do bloco "Controle PWM Space-Vector Baseado em Redes  |          |

|            | ais"                                                           |          |

| 4.8        |                                                                |          |

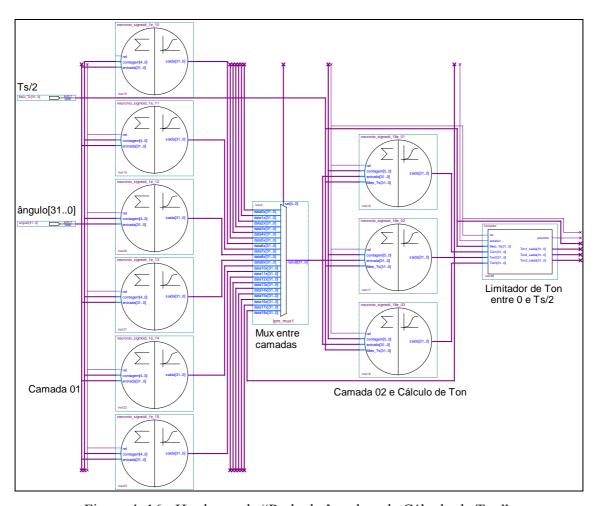

| 4.8        | .2 Módulo "Rede de ângulo e de Cálculo de Ton"                 | 60       |

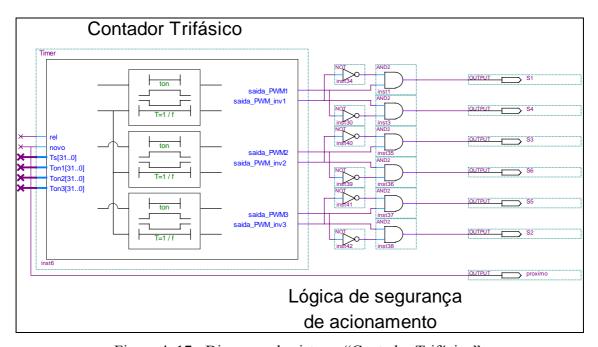

| 4.8   | 8.3 Módulo "Contador Trifásico"            | 62 |

|-------|--------------------------------------------|----|

| 4.9   | Considerações finais                       | 63 |

| CAPÍT | ULO 5 - PROTÓTIPO E RESULTADOS             | 65 |

| 5.1   | Introdução                                 | 65 |

| 5.2   | Especificações do sistema                  | 65 |

| 5.3   | O protótipo                                | 66 |

| 5.4   | Resultados experimentais e de simulação    | 71 |

| 5.5   | Considerações finais                       | 79 |

| CAPÍT | ULO 6 - CONCLUSÕES                         | 80 |

| 6.1   | Conclusões                                 | 80 |

| 6.2   | Propostas para trabalhos futuros           |    |

|       | A: Esquemáticos dos circuitos do protótipo |    |

|       | B: Códigos em VHDL e em C                  |    |

| Anexo | C: Especificações de Componentes           | 20 |

| REFER | LÊNCIAS BIBLIOGRÁFICAS                     | 24 |

### LISTA DE FIGURAS

| Figura 2. 1 - Diagrama do controlador proposto.                                        | 8    |

|----------------------------------------------------------------------------------------|------|

| Figura 2. 2 - Aspecto físico de um motor de indução.                                   | 9    |

| Figura 2. 3 - Módulo "Inversor Baseado em IGBT".                                       |      |

| Figura 2. 4 - Diagrama do subsistema "Laços de Controle de Torque e Fluxo"             |      |

| Figura 2. 5 - Subsistema "Vector Rotator".                                             |      |

| Figura 2. 6 - Diagrama do Controle PWM Space-Vector Baseado em Redes Neurais.          | . 19 |

| Figura 2. 7 - Exemplo de geração de sinais PWM.                                        |      |

|                                                                                        |      |

| Figura 3. 1 - Gráficos de tempo de ativação gerados por SVM. 23                        |      |

| Figura 3. 2 - Diagrama do Controle PWM Space-Vector Baseado em Redes Neurais.          |      |

| Figura 3. 3 - Interconexão das saídas PWM com inversor de potência e MIT               |      |

| Figura 3. 4 - Redes recorrente e MLP compondo a "RNN-MLP".                             | . 26 |

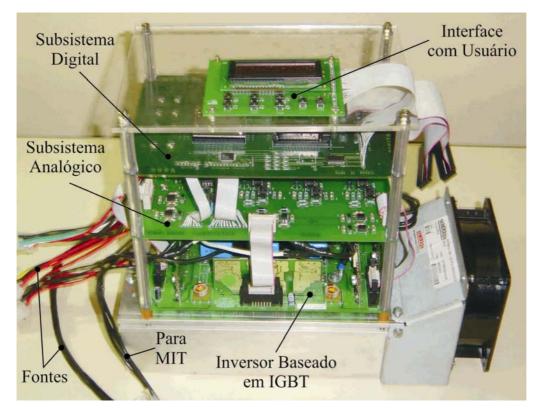

| Figura 4. 1 - Protótipo do controlador do MIT baseado em redes neurais                 | 30   |

| Figura 4. 2 - Medição de tensão de entrada da MIT.                                     |      |

| Figura 4. 3 - Medição de corrente                                                      |      |

| Figura 4. 4 - Interligação com o conversor ADS8364                                     | 34   |

| Figura 4. 5 - Unidade "Interface com ADS", dentro do FPGA                              |      |

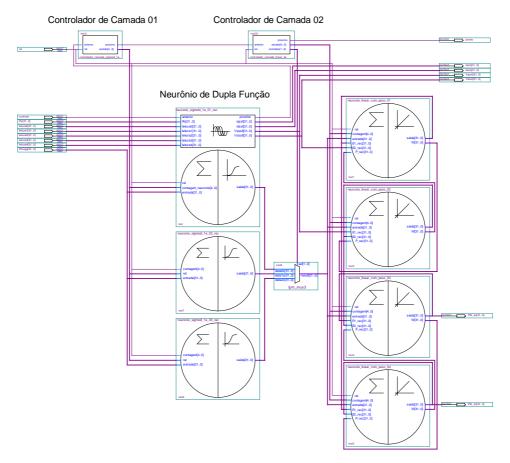

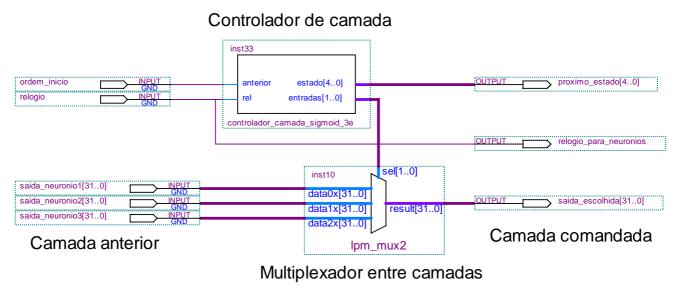

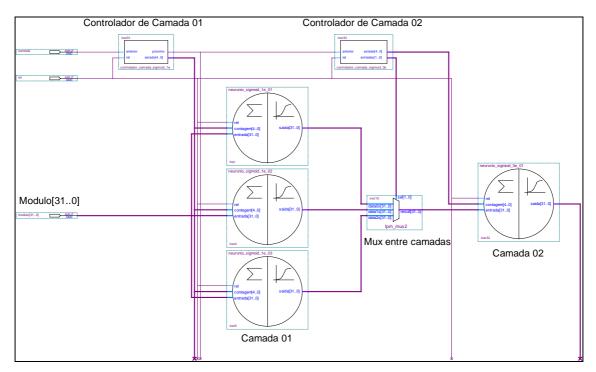

| Figura 4. 6 - Rede híbrida "RNN-MLP" no FPGA.                                          |      |

| Figura 4. 7 - Interconexões do controlador de camada em uma rede neural                |      |

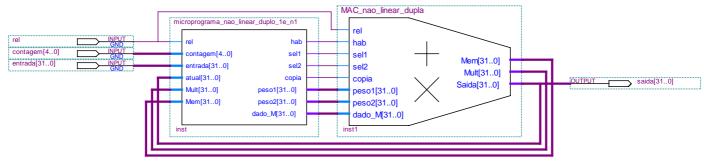

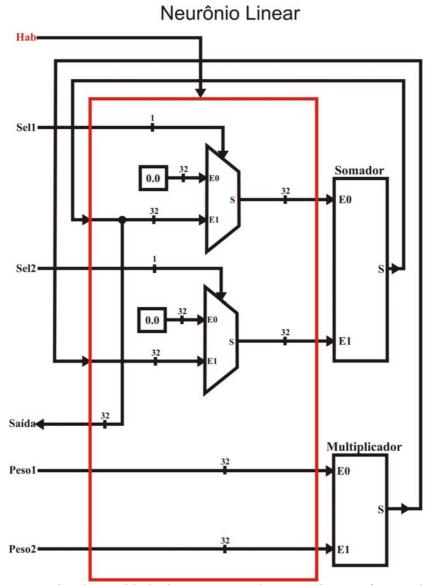

| Figura 4. 8 - Diagrama do neurônio de 1 entrada e com função de ativação linear        |      |

|                                                                                        |      |

| Figura 4. 9 - Interior da "Unidade de Execução" do neurônio com função de ativação     |      |

| linear.                                                                                |      |

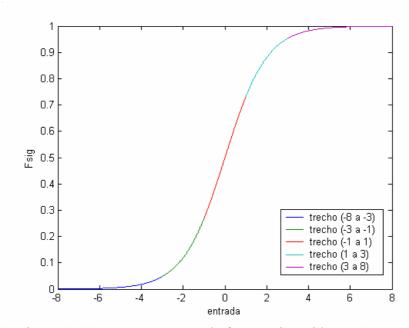

| Figura 4. 10 - Representação da função sigmóide por "Spline".                          |      |

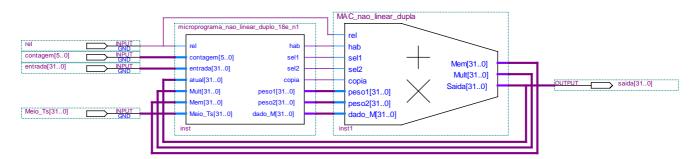

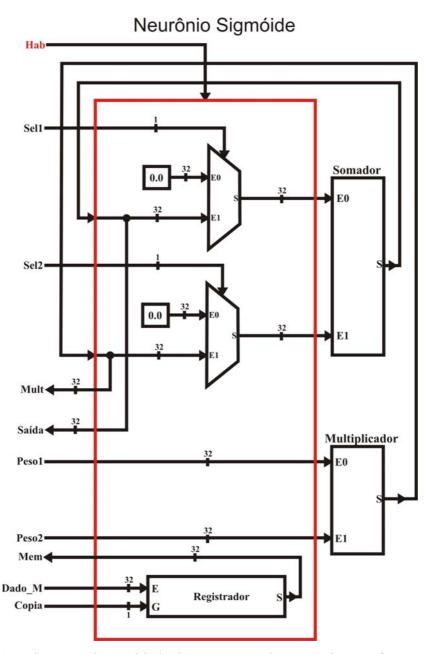

| Figura 4. 11 - Neurônio digital com função de ativação sigmóide                        |      |

| Figura 4. 12 - Diagrama da "Unidade de Execução" do neurônio com função sigmóid        |      |

| Eigens 4 12 Linkon do adding gamagantan do a blood "Estimadar do Cincia"               |      |

| Figura 4. 13 - Linhas de código representando o bloco "Estimador de Sinais"            |      |

| Figura 4. 14 - Código de programação do bloco "Controlador".                           |      |

| Figura 4. 15 - Estrutura da "Rede de módulo" no FPGA.                                  |      |

| Figura 4. 16 - Hardware da "Rede de ângulo e de Cálculo de Ton".                       |      |

| Figura 4. 17 - Diagrama do sistema "Contador Trifásico"                                | . 62 |

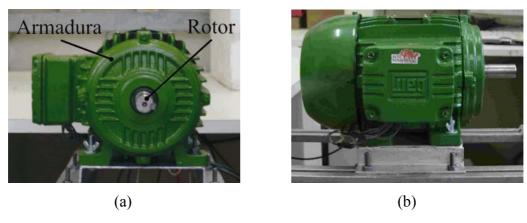

| Figura 5. 1 - Motor de indução trifásico (MIT) utilizado.                              | . 66 |

| Figura 5. 2 - Visão do protótipo do controlador de MIT                                 |      |

| Figura 5. 3 - Placa de circuito da "Interface com Usuário".                            | . 67 |

| Figura 5. 4 - Placa do "Subsistema Digital".                                           |      |

| Figura 5. 5 - Placa do "Subsistema Analógico"                                          |      |

| Figura 5. 6 - Módulo "Inversor Baseado em IGBT".                                       |      |

| Figura 5. 7 - Fonte de alimentação do protótipo                                        |      |

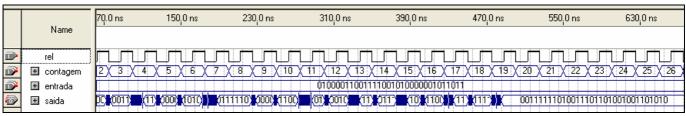

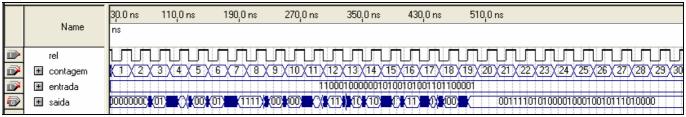

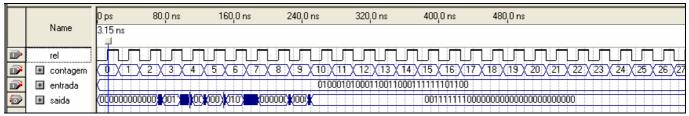

| Figura 5. 8 - Valor 0.8078 aproximado em formato IEEE 754.                             | . 71 |

| Figura 5. 9 - Saída = 0.8078, para uma entrada sem normalização x =188.62638.          |      |

| Latência do neurônio próxima de 500ns.                                                 | . 72 |

| Figura 5. 10 - Saída = $0.0474$ , para uma entrada sem normalização x = $-553.30284$ . |      |

| Latência do neurônio próxima de 500ns.                                                 | . 72 |

| Figura 5. 11 - Saída = 1.0 (comportamento no mais infinito), resultado de uma entrado  |      |

| não normalizada x =2456.99536. Latência do neurônio próxima de 250ns                   |      |

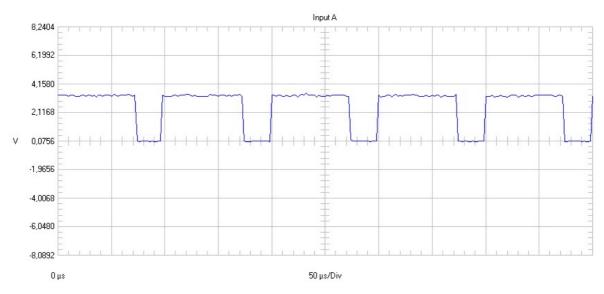

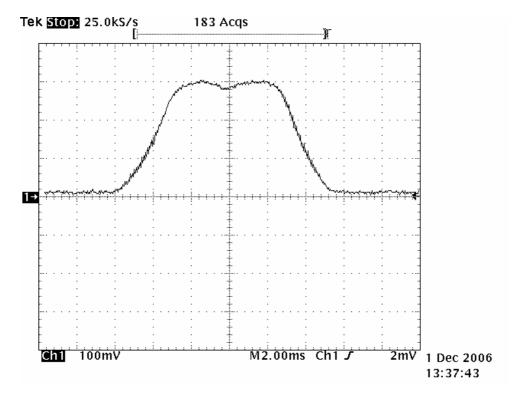

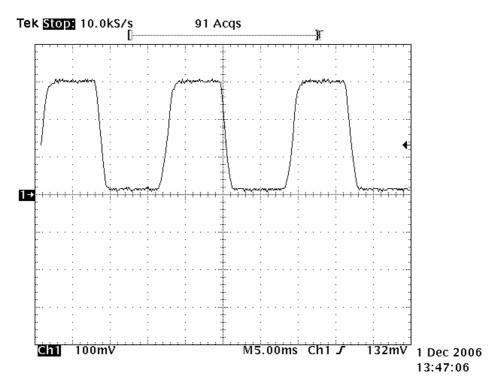

| Figura 5. 12 - Sinal PWM na fase A do inversor.                                        |      |

| <u> </u>                                                                               |      |

| Figura 5. 13 - Sinal PWM na fase B do inversor                                      | 74 |

|-------------------------------------------------------------------------------------|----|

| Figura 5. 14 - Sinal PWM na fase C do inversor                                      | 74 |

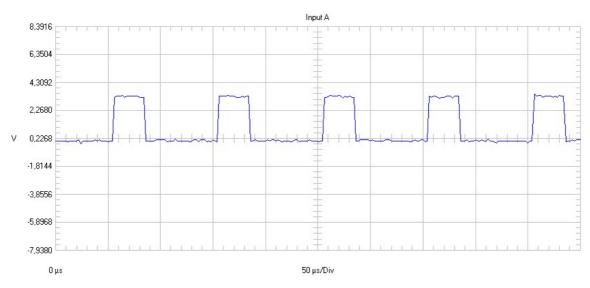

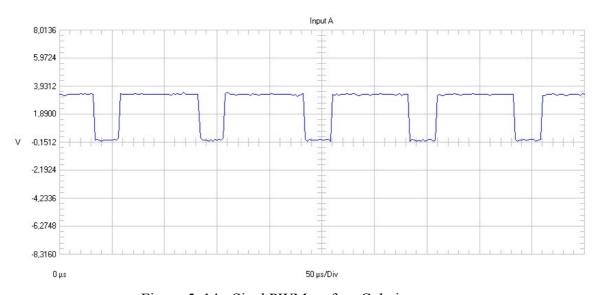

| Figura 5. 15 - Exemplo de formas de onda de tempo de T <sub>on</sub> para região de |    |

| submodulação.                                                                       | 75 |

| Figura 5. 16 - Exemplo de formas de onda de tempo de T <sub>on</sub> para região de |    |

| sobremodulação-modo 1                                                               | 75 |

| Figura 5. 17 - Exemplo de formas de onda de tempo de T <sub>on</sub> para região de |    |

| sobremodulação-modo 2                                                               | 76 |

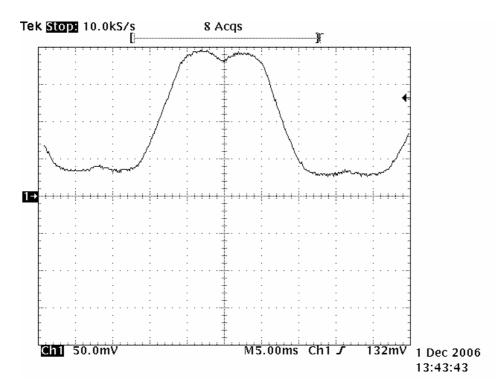

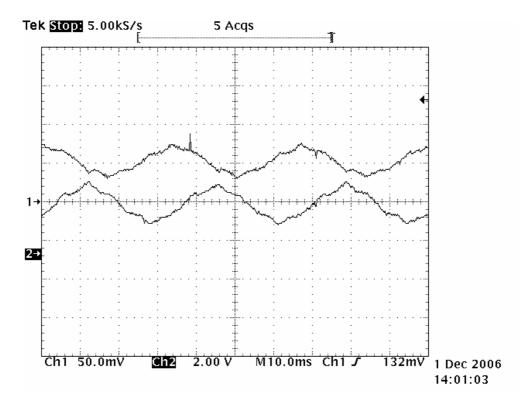

| Figura 5. 18 - Tensões em duas fases do motor de indução.                           | 77 |

| Figura 5. 19 - Corrente da fase B do motor de indução                               | 77 |

| Figura 5. 20 - Corrente da fase C do motor de indução                               | 78 |

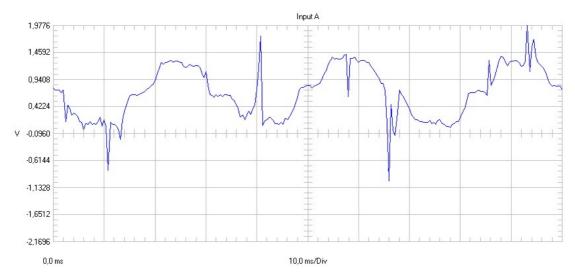

| Figura 5. 21 - Simulação de estimação de fluxo do MIT.                              | 79 |

| Figura 6. 1. Dados de utilização global do FPGA Stratix 2.                          | 81 |

### LISTA DE TABELAS

| Tabela 4. 1 - Codificação em 16 bits das entradas analógicas do ADS8364              | . 35 |

|--------------------------------------------------------------------------------------|------|

| Tabela 4. 2 - Microprograma da "Unidade de Decisão" do neurônio com função de        |      |

| ativação linear.                                                                     | . 44 |

| Tabela 4. 3 - Microprograma da "Unidade de Decisão" do neurônio com função sigmóide. |      |

| Tabela 5. 1 - Especificações do sistema.                                             | . 65 |

#### LISTA DE SÍMBOLOS

CA: Corrente alternada.

CC: Corrente contínua.

DSK: DSP Starter Kit.

DSP: Digital Signal Processor.

EDMA: Extended Direct Memory Access.

EMIF: External Memory Interface.

FPGA: Field Programmable Gate Array.

IGBT: Insulated Gate Bipolar Transistor.

LCD: Liquid Crystal Display.

MAC: multiplicador-acumulador.

MLP: Multi Layer Perceptron.

MIT: Motor de Indução Trifásico.

PCLPF: Programmable Cascaded Low Pass Filter.

PLL: Phase Locked Loop.

PWM: Pulse Width Modulation (Modulação por Largura de Pulso).

ROM: Read Only Memory.

RNA: Rede Neural Artificial.

RNN: Recurrent Neural Network (Rede Neural Recorrente).

SDRAM: Synchronous Dynamic Random Access Memory.

SVM: Space-Vector Modulação por Vetores Espaciais).

UCP: Unidade Central de Processamento.

ULA: Unidade Lógica e Aritmética.

VHDL: VHSIC Hardware Description Language.

VHSIC: Very High Speed Integrated Circuit.

VLWI: Very Large Word Instruction.

# CAPÍTULO 1 – INTRODUÇÃO

#### 1.1 Introdução

Este capítulo visa fornecer um embasamento conceitual sobre o tema de acionamento de motores de indução. Inicialmente, é feita uma revisão bibliográfica sobre máquinas de indução e sobre suas técnicas de acionamento. A seguir, são descritas as técnicas escalar e vetorial para controle de motores e a utilização da inteligência artificial como ferramenta útil na implementação em hardware de sistemas para acionamento de máquinas CA. Finalizando, é apresentada a ordem em que estão organizados os capítulos deste trabalho, além do assunto que os aborda. A seção a seguir inicia com uma breve revisão sobre máquinas de indução e seu acionamento em velocidades variáveis.

#### 1.2 O motor de indução e o acionamento em velocidades variáveis

Por um longo tempo, a máquina de indução foi, tradicionalmente, utilizada em aplicações de velocidades constantes e em acionamentos de baixo desempenho, devido às suas características não-lineares, multivariáveis e complexidade nos algoritmos de controle [1].

Desta forma, quando se pensava em acionamentos com velocidade variável, optava-se por utilizar a máquina de corrente contínua, cujas características de desacoplamento entre o fluxo (campo) e o conjugado (armadura) permitem um controle independente da velocidade, possibilitando um excelente desempenho nesse tipo de aplicação [2].

Todavia, as máquinas de corrente contínua têm custos elevados, necessitam de manutenções freqüentes e tornam-se inviáveis para certas aplicações. Ao contrário, a máquina de indução possui construção robusta, menor custo de fabricação e manutenção. A partir da década de 70, com o surgimento da teoria de controle vetorial (princípio de orientação de campo) [3] é que se obteve uma modelagem adequada para o controle mais preciso das máquinas de corrente alternada. Somado ao contínuo avanço da eletrônica de potência, a partir da década de 80, a máquina de indução vem

dominando o mercado de acionamentos em velocidades variáveis e alto desempenho [4].

#### 1.3 O controle da máquina de indução: escalar e vetorial

Inicialmente, o controle da máquina de indução foi tido como escalar, em que se varia, proporcionalmente, tensão e freqüência estatórica, mantendo-se o fluxo de entreferro da máquina constante, não se alterando o torque máximo. Trata-se de um controle relativamente simples, utilizado em sistemas de acionamento em que não se necessite de grandes variações de velocidades e com rápidas respostas e alta eficiência [5].

A técnica de orientação de campo possibilita um desacoplamento entre o conjugado eletromagnético e o fluxo (campo) na máquina de corrente alternada, semelhante à máquina CC com excitação em separado, melhorando assim, suas características dinâmicas, quando comparada com a resposta dos acionamentos convencionais. Isto é conseguido através da definição de um eixo de referência *q-d* que gira sincronamente com o vetor espacial *fluxo de rotor*. Desta forma, o torque é controlado através da componente *q* do vetor espacial da corrente de estator e simultaneamente, o fluxo é controlado através da componente *d* do vetor espacial da corrente de estator.

Sua implementação só foi possível a partir da década de 80, com os avanços da eletrônica de potência, de microprocessadores e o surgimento da tecnologia de processadores digitais de sinais (DSP), já que esta técnica necessita de alta complexidade computacional.

Vários métodos de implementação têm sido desenvolvidos, e estas técnicas podem ser classificadas baseadas no modo usado para se determinar o vetor de fluxo rotórico ou estatórico, dentre as quais se destacam:

- Controle por orientação de campo direto: a posição e a magnitude do fluxo rotórico são medidas ou estimadas através de um observador de estado não linear. A desvantagem é que se deve ter um conhecimento, a priori, da constante de tempo elétrica do rotor, a qual varia com a temperatura, frequência e saturação.

- Controle de campo orientado indireto (COI): a estimação do fluxo de referência (fluxo de rotor) é feita em malha aberta e possui como vantagens: simplicidade

do modelo obtido, boa resposta dinâmica [6, 7]. Uma desvantagem é que a estimação do fluxo depende dos parâmetros da máquina e seu uso incorreto pode causar o acoplamento das equações de torque e fluxo, degradando o desempenho do controle [8, 9].

- Controle Direto de Torque (DTC) e Auto-Controle Direto (DSC): técnicas que se baseiam no controle direto e independente do torque e do fluxo do motor CA, possibilitando rápida resposta de torque e excelente regulação de velocidade [10, 11].

- Controle Robusto e Adaptativo: são técnicas utilizadas para controlar plantas ou

processos com incertezas. O Controle a Estrutura Variável (VSC) com modos

deslizantes é um tipo de controle robusto, foi proposto na década de 50 e há

diversas contribuições na aplicação de acionamentos e controle de máquinas de

indução [12, 13, 14].

#### 1.4 Técnicas de controle inteligente

Dentre as técnicas de inteligência artificial aplicadas ao acionamento de máquinas de indução, destacam-se: controle baseado em redes neurais artificiais, controle fuzzy, controle neuro-fuzzy e controle baseado em algoritmos genéticos.

A lógica nebulosa ou fuzzy [15, 16] proporcionou o desenvolvimento de controladores fuzzy, em que algoritmos convertem estratégias de controle baseadas no conhecimento de especialistas em estratégias de controle automático, apresentando resultados superiores àqueles com controle convencional.

A técnica de Algoritmos Genéticos também pode ser utilizada no controle de motores [17]. Dentre as aplicações destacam-se: projeto de estimadores de fluxos para se obter os parâmetros ótimos do controle vetorial de um MI [18], na sintonia de controladores fuzzy, determinação dos parâmetros elétricos de um motor de indução através de técnicas de estimação de parâmetros, etc.

Redes Neurais Artificiais também têm sido uma das ferramentas muito utilizadas na identificação e controle de sistemas dinâmicos não-lineares [19], devido a sua habilidade de aprendizagem e melhorar progressivamente a *performance* de sistemas de controle [20, 21]. A rede neural ainda pode ser combinada com a técnica de lógica fuzzy, surgindo os controladores neuro-fuzzy (ou híbridos). A melhor vantagem sobre os controladores fuzzy convencionais é que a função de pertinência e as regras são

produzidas por um processo automático [22], minimizando a intervenção humana no processo de sintonia.

Desta forma, a aplicação de inteligência artificial em acionamentos de máquinas melhora satisfatoriamente a performance, tornando o sistema mais robusto à variações dos parâmetros e da carga.

Quando se trata de controle *on-line* de máquinas de indução para altos desempenhos, a informação da velocidade é necessária e isto pode ser conseguido através de sua medição direta (*encoder*) ou sua estimação através da medição de tensão e corrente (*sensorless*). Muitos trabalhos foram desenvolvidos com a aplicação da técnica de redes neurais para estimar velocidade, fluxos ou corrente estatórica na máquina de indução [23, 24].

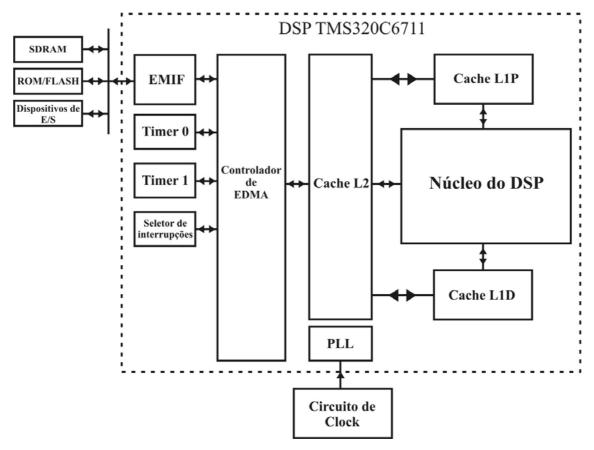

Atualmente, com o desenvolvimento dos DSP's, as técnicas de controle inteligente de motores de indução (especialmente as redes neurais) podem ser implementadas como sistemas de tempo real. Porém, para implementá-las em hardware, neurônios com altas capacidades de processamento são necessários. A seção a seguir apresenta maiores detalhes sobre o tema da implementação de redes neurais em hardware.

#### 1.5 Implementação de redes neurais artificiais (RNA) em hardware

Um dos problemas na implementação de redes neurais em hardware para o controle e acionamento de MI está na complexidade de se representar eletronicamente funções de ativação não-lineares. Muitos modelos de redes neurais foram desenvolvidos com neurônios binários, ou seja, neurônios com entradas e saídas que podem assumir apenas dois valores (-1 e 1 ou 0 e 1).

De fato, em muitas implementações utilizam-se funções de ativação *hard-limit* ou funções lineares saturadas, com a finalidade de evitar a complexidade envolvida na construção de uma função de ativação sigmoidal. O problema desta abordagem está no modelo distanciar-se demasiadamente da complexidade do neurônio biológico [25]. Estas e outras desvantagens encontradas nos primeiros modelos binários foram superadas pelo neurônio analógico. Neurônios implementados com circuitos analógicos são rápidos e possuem reduzida complexidade, permitindo a construção de redes neurais com grande densidade de neurônios e baixo tempo de resposta. Entretanto, a implementação de neurônios analógicos possui algumas desvantagens, tais como: baixa

imunidade a ruídos elétricos e a necessidade do uso de resistores de alta precisão para representação dos pesos sinápticos [26, 27].

Devido a tais problemas, pesquisas voltadas a implementação de redes *multi-layer perceptron* (MLP's) para emulação do comportamento do neurônio biológico têm atraído a atenção da comunidade científica [28, 29, 30]. Alguns autores implementaram uma rede MLP com funções de ativação lineares [31], outros [32] implementaram uma rede neural para identificar, em tempo real, a velocidade do motor, também utilizando funções lineares para modelar neurônios digitais.

Este trabalho tem como contribuição a implementação dos neurônios artificiais como processadores digitais independentes, utilizando funções de ativação sigmoidais representadas em hardware por interpolação. Para permitir reduzidos erros de representação numérica nos cálculos, os neurônios trabalham com valores em ponto flutuante de 32 bits (IEEE 754). A estrutura e o conteúdo dos capítulos deste trabalho são apresentados na seção a seguir.

#### 1.6 Descrição dos capítulos

Esta dissertação possui seis capítulos e as descrições de cada um deles segue abaixo:

- Capítulo 2: apresenta o equacionamento da máquina de indução com orientação de campo de estator, bem como a visão geral do sistema de acionamento. O capítulo apresenta os dois subsistemas compondo o controlador do motor deste trabalho: um subsistema de potência e um de processamento de sinais.

- Capítulo 3: detalha a estrutura interna dos subsistemas "Estimador de Fluxo" e

"Controle PWM Space-Vector Baseado em Redes Neurais", descritos de forma geral no capítulo 2. Estes subsistemas representam duas redes neurais artificiais modeladas nos trabalhos [25] e [26] e que serviram de base para a implementação proposta neste trabalho.

- Capítulo 4: detalha arquitetura de hardware do protótipo do controlador do motor de indução proposto neste trabalho, ou seja, como são os circuitos representando todos os subsistemas modelados matematicamente conforme apresentado nos capítulos 2 e

3. O capítulo utiliza linguagem de descrição de hardware (VHDL) e de programação de alto nível (C) para explicar como são e como funcionam as plataformas de

implementação utilizadas na construção do protótipo, ou seja: um DSP (processador digital de sinais) e um FPGA (*Field Programmable Gate Array*).

- Capítulo 5: faz a apresentação do protótipo final e de resultados experimentais obtidos. O capítulo inclui fotos das placas de circuito impresso do protótipo, além de formas de onda obtidas em testes de funcionamento realizados com o protótipo.

- Capítulo 6: destina-se à apresentação das conclusões finais e de propostas para futuros trabalhos.

#### 1.7 Considerações finais

Este capítulo fez uma breve revisão bibliográfica sobre acionamento de motores de indução, implementação em hardware de redes neurais artificiais e sobre a ordem como estão apresentados os capítulos deste trabalho. O objetivo principal foi situar o leitor sobre alguns desafios e perspectivas existentes na área de controle inteligente de motores de indução. Ao final do trabalho, espera-se que o leitor adquira uma visão global dos conceitos e das soluções utilizadas na implementação do controlador do motor proposto.

# CAPÍTULO 2 - CONTROLE DE MOTOR DE INDUÇÃO COM ORIENTAÇÃO DO CAMPO ESTATÓRICO

#### 2.1 Introdução

A proposta deste trabalho é a implementação em hardware de um controlador do motor de indução trifásico, utilizando como base uma modelagem de sistema idealizada em trabalhos anteriores. Este capítulo apresenta esta modelagem a partir da qual foi criada uma arquitetura de hardware, descrita em maiores detalhes no capítulo 4. Inicialmente é apresentada uma visão geral dos blocos compondo a estrutura do sistema, e então, cada bloco é apresentado separadamente O objetivo do capítulo é a apresentação do sistema discutindo somente a função e o equacionamento dos seus blocos constituintes.

A seção a seguir inicia o capítulo com uma descrição estrutural geral do controlador de motor de indução proposto.

#### 2.2 Visão geral do sistema

Conforme descrito no capítulo 1, existem várias abordagens retratadas na literatura para controle inteligente de motores de indução. O controlador de motor proposto neste trabalho entra na categoria de controle inteligente de máquinas de indução, por ser baseado no uso de redes neurais artificiais, uma das áreas de estudo da Inteligência Artificial.

Iniciando pela apresentação geral do sistema de controle de motor de indução, a figura 2.1 mostra um diagrama geral do sistema previamente modelado nos trabalhos anteriores [25] e [26]. Este sistema representa um controle em malha fechada "sensorless". Isto significa um controle de motor baseado na estimação de grandezas da máquina controlada e não no sensoriamento ou medição direta destas grandezas. Uma das principais grandezas a ser estimada pelo sistema é o fluxo estatórico do motor. A partir desta grandeza, podem-se estimar vários outros parâmetros úteis em um controle inteligente do motor de indução.

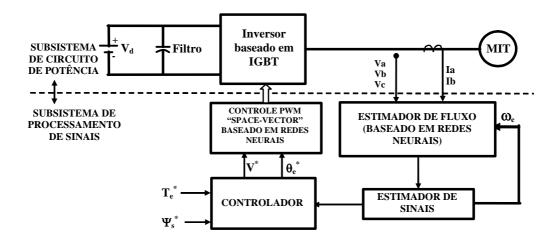

Figura 2. 1 - Diagrama do controlador proposto.

De acordo com a figura 2.1, o sistema é constituído de dois subsistemas, um "Subsistema de circuito de potência" (acima da linha tracejada), e um "Subsistema de processamento de sinais" (abaixo da linha tracejada).

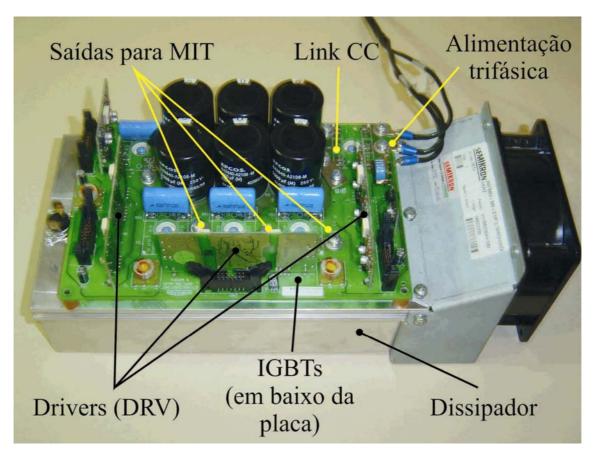

O propósito do "Subsistema de circuito de potência" é transformar energia elétrica armazenada no "Link CC" (fonte "V<sub>d</sub>" mais "Filtro") em energia mecânica rotacional, entregue ao motor de indução trifásico (MIT). Esta transformação está centrada no trabalho do módulo localizado entre o "Link CC" e o "MIT", ou seja, o "Inversor baseado em IGBT". Este módulo representa um conversor CC/CA de potência, trifásico, e controlado por sinais PWM (Modulação por Largura de Pulso) providos pelo "Sistema de processamento de sinais".

O "Subsistema de processamento de sinais" representa o foco deste trabalho. Ele representa a parte digital do controlador do motor de indução trifásico, sendo baseado em redes neurais artificiais. É composto pelos módulos "Controlador", "Controle PWM Space-Vector Baseado em Redes Neurais", "Estimador de Fluxo" e pelo "Estimador de Sinais".

Aprofundando um pouco mais a análise sobre cada um dos dois subsistemas apresentados nesta visão geral, a seção a seguir inicia descrevendo aspectos do "Subsistema de circuito de potência".

#### 2.3 Subsistema de circuito de potência

Embora não seja o foco deste trabalho, é necessária uma descrição das principais características dos elementos compondo o "Subsistema de circuito de potência". Este

subsistema representa a parte de potência do controlador proposto neste trabalho, estando sob controle do "Subsistema de processamento de sinais". A seção a seguir inicia apresentando a estrutura e o funcionamento do "Motor de indução trifásico".

#### 2.3.1 Motor de indução trifásico

O elemento eletro-mecânico do sistema, transformador de potência elétrica em potência mecânica, é o motor de indução trifásico (MIT). Um MIT é equivalente a um transformador trifásico, porém com enrolamento secundário curto-circuitado e livre para realizar movimento rotacional. Um diagrama construtivo do motor de indução é mostrado na figura 2.2.

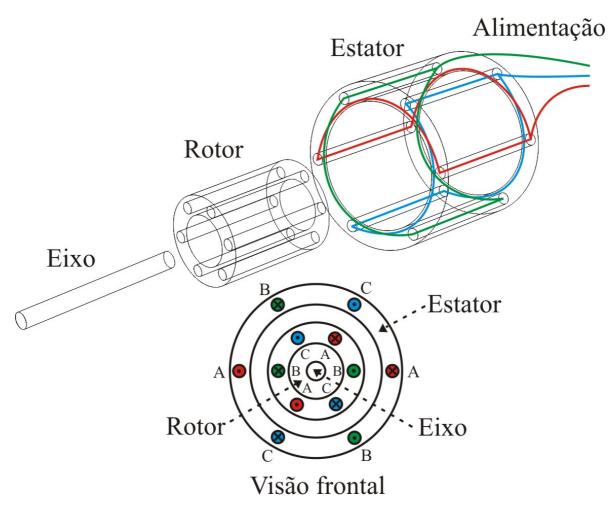

Figura 2. 2 - Aspecto físico de um motor de indução.

A figura 2.2 apresenta uma visão espacial e uma frontal dos elementos básicos que constituem um motor de indução: estator, rotor e o eixo.

Em caso de alimentação trifásica, o estator (ou armadura) é envolvido por três enrolamentos formando dipolos elétricos (bobinas) defasados espacialmente de 120 graus. Na visão frontal da figura 2.2, o estator representa o anel mais externo e os enrolamentos das bobinas representam os círculos coloridos no anel (podendo estar entrando (x) ou saindo (•) do plano da página). O controle das formas de onda de alimentação (tensão e corrente) das bobinas no estator constitui o objetivo final de um controlador do motor de indução. Em muitas aplicações práticas, a alimentação aplicada ao estator consiste de ondas senoidais providas por uma rede trifásica (partida direta), dispensando o uso de um sistema controlador para o motor.

O rotor representa o elemento girante do motor. Na figura 2.2 ele está representado pelo conjunto de barras presas por anéis em suas extremidades, formando o que é conhecido como "gaiola de esquilo". Em alguns tipos de rotores, a estrutura em forma de gaiola é substituída por enrolamentos semelhantes aos do estator, porém, não acessíveis fora do motor. Na visão frontal da figura 2.2, o rotor representa o anel central e os círculos coloridos neste anel representam as barras da gaiola do rotor (sendo percorridas por correntes entrando (×) e saindo (•) do plano da página).

Durante o funcionamento do motor, o rotor gira devido ao torque (conjugado) produzido por uma força magnética aplicada ao rotor. As formas de onda aplicadas às bobinas do estator geram um campo magnético resultante girando em torno do eixo central do motor. A variação de fluxo desse campo magnético induz uma tensão no rotor, esta tensão então acaba gerando correntes rotóricas. Estas correntes, sob a ação do campo magnético do estator, originam a força magnética geradora do torque no rotor. Como consequência, o rotor gira tentando alcançar o campo girante, de modo a diminuir a corrente induzida no rotor (resultado da lei de "Lenz").

Preso ao rotor está o eixo do motor, mostrado como o círculo central na visão frontal da figura 2.2. O eixo simplesmente representa a haste de transmissão da energia mecânica do rotor para cargas externas conectadas ao motor.

Prosseguindo com a apresentação dos circuitos de potência do controlador de MIT deste trabalho, a seção a seguir apresenta o segundo elemento de destaque compondo o "Subsistema de circuito de potência", o módulo "Inversor Baseado em IGBT".

#### 2.3.2 Inversor Baseado em IGBT

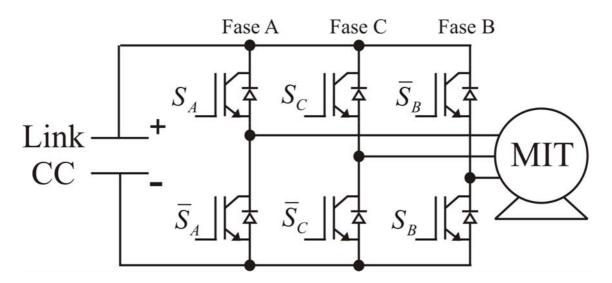

Conforme já mencionado na seção anterior, para que se possa controlar um motor de indução deve-se aplicar em seus terminais de entrada uma forma de onda de alimentação controlada. O módulo "Inversor Baseado em IGBT" representa um circuito de potência para o controle da amplitude e da freqüência das tensões de alimentação aplicadas ao motor. Amplitude e frequência de tensões CA podem ser variadas utilizando diferentes tipos de conversores. O "Inversor Baseado em IGBT" representa um conversor alimentado por fonte de tensão, chaveado e em ponte completa trifásica. Para um melhor entendimento, a figura 2.3 apresenta um diagrama do circuito do inversor utilizado neste trabalho.

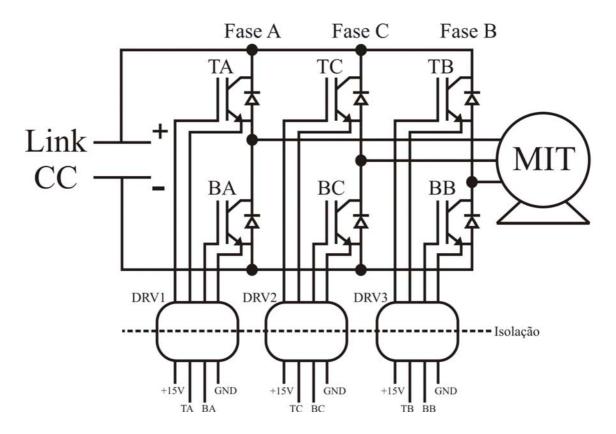

Figura 2. 3 - Módulo "Inversor Baseado em IGBT".

O circuito da figura 2.3 gera uma tensão alternada de saída através do chaveamento de uma tensão CC (Link CC), utilizando, para isto, um circuito composto por três pares de chaves ("pernas" do inversor) interligadas, formando uma ponte completa. Neste caso, as chaves utilizadas são módulos IGBT (Transistor Bipolar de Gate Isolado). Na figura 2.3, os IGBTs estão representados pelas siglas indicando suas posições na ponte: "TA" (topo fase A), "BA" (baixo fase A), "TB" (topo fase B), "BB"

(baixo fase B), "TC" (topo fase C), "BC" (baixo fase C). Por se tratarem de dispositivos de potência, os IGBTs são controlados por meio de circuitos de disparo de comando de pulso de gate ("DRV1", "DRV2", "DRV3", na figura 2.3). Este circuito de disparo representa uma interface de hardware com isolação permitindo que circuitos de controle de baixa potência consigam comandar os IGBTs da ponte. Adicionalmente, este circuito de disparo é capaz de filtrar ruídos dos sinais de chaveamento enviados aos IGBTs e é capaz de gerar um "tempo morto" sempre que duas chaves de uma mesma "perna" do inversor são comutadas ao mesmo tempo, evitando um curto-circuito momentâneo nesta "perna". De acordo com a figura 2.3, cada circuito de disparo deve receber uma alimentação externa de +15V CC e deve receber dois sinais de comando: um para chave de topo (como "TA" para o "DRV1") e outro para chave de baixo (como "BA" para o "DRV1").

Um dos objetivos finais do controle do inversor da figura 2.3, é a construção de tensões alternadas para alimentação do motor, com o mínimo de conteúdo harmônico de baixa frequência, já que altas frequências podem ser eliminadas mais facilmente através de filtros apropriados. A aplicação de uma següência adequada de comutação das chaves da ponte inversora, a cada período de amostragem "T<sub>s</sub>" (inverso da frequência de chaveamento), gera três ondas defasadas de 120 graus, compostas por pulsos, simulando ondas CA senoidais, para alimentação do motor de indução. A amplitude e a frequência destas pseudo-senóides são responsabilidades do controlador externo comandando o inversor, enquanto a técnica utilizada para comutação das chaves da ponte é conhecida como modulação. Neste trabalho a técnica de modulação utilizada é a "Modulação por Vetores Espaciais" (ou "Space-Vector Modulation"), implementada pelos circuitos digitais do "Subsistema de Processamento de Sinais", descrito na seção a seguir.

#### 2.4 Subsistema de Processamento de Sinais

Representando o "cérebro" do controlador de motor de indução deste trabalho, existe o "Subsistema de Processamento de Sinais". A função deste subsistema é comandar o "Subsistema de circuito de potência" a partir do processamento de informações fornecidas pelo usuário e de informações medidas do motor de indução controlado. No protótipo final proposto neste trabalho, o "Subsistema de Processamento de Sinais" é constituído por um DSP (Processador Digital de Sinais) em interação direta com um FPGA (Field Programmable Gate Array).

O funcionamento do "Subsistema de processamento de sinais" é baseado na execução contínua de ciclos de trabalho (iterações). Cada iteração começa com a medição de tensões e correntes trifásicas dos terminais de entrada do MIT. A seguir estes dados sofrem transformações de eixo e são submetidos a uma seqüência de subsistemas composta pelo "Estimador de Fluxo", "Estimador de Sinais", "Controlador", e "Controle PWM Space-Vector Baseado em Redes Neurais". O resultado final de cada iteração é a atualização de parâmetros de temporização de sinais de comando aplicados ao módulo "Inversor de Baseado em IGBT" (Subsistema de circuito de potência). No decorrer desta seção, uma iteração de trabalho do "Subsistema de Processamento de Sinais" é descrita através da apresentação das funções executadas pelos seus blocos constituintes. Inicialmente, na seção a seguir, é descrito o bloco "Estimador de Fluxo".

#### 2.4.1 Bloco Estimador de Fluxo

Durante um ciclo de trabalho, o primeiro bloco a trabalhar é o "Estimador de Fluxo". Sua finalidade é estimar o fluxo de estator atual da máquina de indução usando medições de tensão e corrente dos terminais de entrada da MIT.

Este bloco recebe como entradas as tensões das fases A, B e C  $(V_a, V_b, V_c)$ , e também as correntes das fases A e B  $(i_a, i_b)$ . Em um sistema real, estes sinais são primeiramente condicionados por filtros do tipo passa-baixa para eliminação de ruídos, com correção dos atrasos indesejáveis, antes de serem aplicados às entradas do bloco "Estimador de Fluxo". Dentro do bloco, o primeiro processamento realizado sobre estes sinais é uma transformação dos eixos A-B-C para o eixo estacionário d-q-0, conforme indicado pelas equações 2.1 a 2.3.

$$i_c = -i_a - i_b \tag{2.1}$$

$$\begin{bmatrix} V_{qs}^{s'} \\ V_{ds}^{s'} \end{bmatrix} = \begin{bmatrix} 2/3 & -1/3 & -1/3 \\ 0 & -1/\sqrt{3} & 1/\sqrt{3} \end{bmatrix} \cdot \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$$

(2.2)

$$\begin{bmatrix} i_{qs}^{s'} \\ i_{ds}^{s'} \end{bmatrix} = \begin{bmatrix} 2/3 & -1/3 & -1/3 \\ 0 & -1/\sqrt{3} & 1/\sqrt{3} \end{bmatrix} \cdot \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix}$$

(2.3)

Na equação 2.1 está representada a estimação de corrente da fase C através de uma redundância analítica usando as correntes das fases A e B. Na equação 2.2, as tensões das três fases são convertidas nas grandezas:  $V_{qs}^{s'}$  (projeção sobre eixo q) e  $V_{ds}^{s'}$  (projeção sobre o eixo d). Na equação 2.3 ocorre o mesmo tipo de transformação, porém as correntes das três fases sofrem transformações para as componentes  $i_{qs}^{s'}$  (projeção sobre eixo q) e  $i_{ds}^{s'}$  (projeção sobre eixo d).

As tensões e correntes projetadas para o eixo d-q-0, geradas pelas equações 2.1 a 2.3, são então utilizadas nas equações 2.4 e 2.5.

$$V_{qs}^{s''} = V_{qs}^{s'} - i_{qs}^{s'} \cdot R_s \tag{2.4}$$

$$V_{ds}^{s''} = V_{ds}^{s'} - i_{ds}^{s'} \cdot R_s \tag{2.5}$$

As equações 2.4 e 2.5 representam as tensões de estator da MIT no eixo d-q-0  $(V_{qs}^{s"} \ e \ V_{ds}^{s"})$ , ao serem consideradas as quedas de tensão  $i_{qs}^{s'} \cdot R_s$  e  $i_{ds}^{s'} \cdot R_s$ , devidas à resistência de estator  $R_s$ .

As principais saídas do bloco "Estimador de fluxo" são as estimações do fluxo de estator nos eixos d e q, obtidas matematicamente por meio das integrações representadas pelas equações 2.6 e 2.7.

$$\Psi_{ds}^{s} = \int V_{ds}^{s"} dt \tag{2.6}$$

$$\Psi_{qs}^{s} = \int V_{qs}^{s"} dt \tag{2.7}$$

No sistema proposto neste trabalho as integrações das equações 2.6 e 2.7 são realizadas utilizando redes neurais agindo como um filtro passa-baixa programável. Mais especificamente, utiliza-se uma RNN-MLP (rede neural recorrente híbrida com rede *Multi Layer Perceptron*) a ser detalhadamente descrita no próximo capítulo. Esta rede além das entradas  $V_{qs}^{s"}$  e  $V_{ds}^{s"}$  utiliza a entrada  $\omega_e$  (freqüência), calculada pelo bloco "Estimador de Sinais" (descrito na seção seguinte). A estrutura da rede RNN-MLP utilizada realiza integrações sem erro de "*offset*", além de efetuar compensações de deslocamentos de fase gerados pela filtragem analógica dos sinais de tensões e correntes trifásicas (entradas do bloco "Estimador de Fluxo").

Como saída final, além dos valores de fluxo estimado ( $\psi_{qs}^s$  e  $\psi_{ds}^s$ ), o bloco "Estimador de Fluxo" disponibiliza para o próximo bloco no sistema (o "Estimador de Sinais") as correntes  $i_{qs}^{s'}$  e  $i_{ds}^{s'}$ , necessárias neste último bloco.

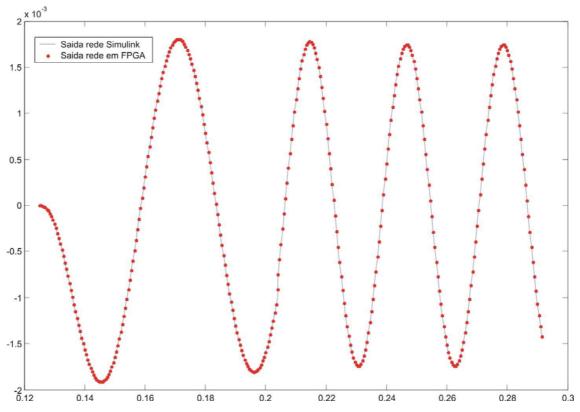

No protótipo final proposto neste trabalho, o bloco "Estimador de Fluxo" foi inserido dentro do FPGA como uma estrutura interligada de processadores, constituindo uma rede neural. Maiores detalhes sobre como este bloco foi implementado em hardware digital são fornecidos no capítulo 4. Resultados experimentais e simulações do funcionamento deste bloco são apresentados no capítulo 5.

#### 2.4.2 Bloco Estimador de Sinais

Este bloco realiza os cálculos com os sinais produzidos pelo bloco "Estimador de Fluxo", listados nas equações 2.8 a 2.16.

$$\hat{\psi}_{s} = \sqrt{(\psi_{ds}^{s})^{2} + (\psi_{as}^{s})^{2}}$$

(2.8)

$$\Theta_e = \sin^{-1}(\psi_{as}^s / \hat{\psi}_s) \tag{2.9}$$

$$i_{ds} = i_{as}^{s'} \cdot \cos \Theta_e - i_{ds}^{s'} \cdot \sin \Theta e \tag{2.10}$$

$$i_{as} = i_{as}^{s'} \cdot \sin \Theta_e + i_{ds}^{s'} \cdot \cos \Theta e \tag{2.11}$$

$$i_{dq} = \left(\frac{\sigma \cdot L_s \cdot i_{qs}^2}{\psi_{ds} - \sigma \cdot L_s \cdot i_{ds}}\right)$$

(2.12)

$$\psi_{ds} = \psi_{as}^{s} \cdot \cos\Theta_{e} - \psi_{ds}^{s} \cdot \sin\Theta e \qquad (2.13)$$

$$\psi_{qs} = \psi_{qs}^{s} \cdot \sin \Theta_{e} + \psi_{ds}^{s} \cdot \cos \Theta e \qquad (2.14)$$

$$T_e = \frac{3 \cdot P}{4} \cdot \left[ \psi_{ds} \cdot i_{qs} - \psi_{qs} \cdot i_{ds} \right] \tag{2.15}$$

$$\omega_{e} = \frac{\left[V_{qs}^{s''} \cdot \psi_{ds}^{s} - V_{ds}^{s''} \cdot \psi_{qs}^{s}\right]}{\hat{\psi}_{s}^{2}}$$

(2.16)

A equação 2.8 representa a obtenção do fluxo de estator ( $\hat{\psi}_s$ ) através do cálculo do módulo do vetor representado pelas coordenadas de eixo estacionário ( $\psi_{qs}^s$  e  $\psi_{ds}^s$ , calculados nas equações 2.6 e 2.7). Na equação 2.9 é obtido o ângulo de rotação estimado  $\Theta_e$  através do arco-seno do valor de fluxo de eixo estacionário q ( $\psi_{qs}^s$ ) dividido pelo fluxo calculado em 2.8. As equações 2.10 e 2.11 estimam as correntes em eixo girante ( $i_{qs}$  e  $i_{ds}$ ) a partir do ângulo de rotação obtido na equação 2.9 e dos valores de corrente ( $i_{qs}^s$  e  $i_{ds}^s$ ) já calculados nos primeiros estágios do bloco anterior ("Estimador

de Fluxo"). As equações 2.13 e 2.14 também utilizam o ângulo  $\Theta_e$ , porém juntamente com os fluxos de estator ( $\psi_{qs}^s$  e  $\psi_{ds}^s$ ), obtêm-se valores de fluxo de estator no eixo girante ( $\psi_{qs}$  e  $\psi_{ds}$ ). A equação 2.12 computa o valor da corrente de compensação de desacoplamento ( $i_{dq}$ ) utilizando o fluxo obtido na equação 2.13 ( $\psi_{ds}$ ), as correntes obtidas nas equações 2.10 e 2.11 ( $i_{qs}$  e  $i_{ds}$ ), e utilizando os parâmetros do MIT predefinidos:  $L_s' = \sigma \cdot L_s$  (indutância transitória de estator). Na equação 2.15 é calculado o torque (conjugado) da máquina considerando o número de pólos da máquina (P), além dos fluxos  $\psi_{ds}$  e  $\psi_{qs}$  (calculados nas equações 2.13 e 2.14) e das correntes obtidas nas equações 2.10 e 2.11 ( $i_{qs}$  e  $i_{ds}$ ). Por fim, na equação 2.16, é calculada a frequência de rotação do motor ( $\omega_e$ ), a partir do quadrado do módulo do fluxo de estator ( $\hat{\psi}_s$ ), dos fluxos ( $\psi_{qs}^s$  e  $\psi_{ds}^s$ ), e das tensões transformadas ( $V_{qs}^{s"}$  e  $V_{ds}^{s"}$ ) calculadas conforme as equações 2.4 e 2.5 pelo bloco anterior (o "Estimador de Fluxo"). Este sinal de frequência ( $\omega_e$ ) volta para o bloco "Estimador de Fluxo", como já mencionado, para atualização dos valores das grandezas estimadas por este bloco.

Como pode ser observado, é extensa a carga de cálculos a ser realizada pelo "Estimador de Sinais". Várias são as formas de implementação em hardware deste bloco. Maiores detalhes referentes à implementação do bloco "Estimador de Sinais" neste trabalho são apresentados no capítulo 4. As saídas deste bloco são direcionadas para o bloco "Controlador", descrito em maiores detalhes na seção a seguir.

#### 2.4.3 Bloco Controlador

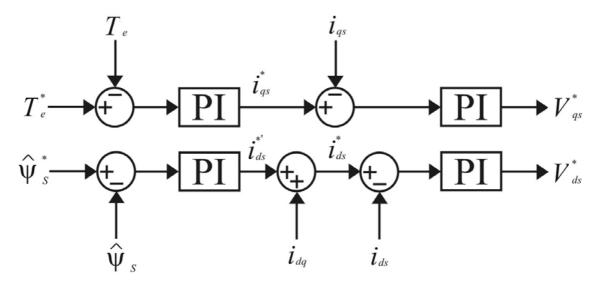

O bloco "Controlador" representa um ponto de convergência do sistema de controle de motor de indução. Este bloco recebe tanto sinais de retroação providos pelo bloco "Estimador de Sinais" ( $T_e$ ,  $\hat{\psi}_s$ ,  $i_{dq}$ ,  $i_{qs}$  e  $i_{ds}$ ), quanto o sinal de torque desejado ( $T_e^*$ ) e de fluxo desejado ( $\hat{\psi}_s^*$ ) fornecidos pelo usuário do sistema. Estes sinais estão representados na figura 2.4 compondo o subsistema "Laços de Controle de Torque e Fluxo" pertencente ao bloco "Controlador".

Figura 2. 4 - Diagrama do subsistema "Laços de Controle de Torque e Fluxo".

O subsistema da figura 2.4 é composto por um laço de controle de torque que inicialmente gera um valor de erro entre o torque estimado  $(T_e)$  e o torque desejado  $(T_e^*)$ . Este sinal de erro entra em um controlador "PI" (proporcional e integral), o qual gera um valor de corrente de estator desejado  $(i_{qs}^*)$ . A diferença entre a corrente desejada  $(i_{qs}^*)$  e a estimada  $(i_{qs})$  representa a entrada de um segundo controlador "PI". A saída deste segundo "PI" representa a tensão desejada de estator no eixo girante q  $(V_{qs}^*)$ .

O segundo laço compondo o subsistema da figura 2.4 inicia gerando um sinal de erro entre o fluxo desejado pelo usuário  $(\hat{\psi}_s^*)$  e o fluxo estimado pelo sistema  $(\hat{\psi}_s)$ . De forma análoga ao primeiro laço, um controlador "PI" gera uma corrente desejada  $(i_{qs}^*)$  de primeiro estágio. Esta corrente, no estágio seguinte, é adicionada com  $i_{dq}$  (corrente de compensação de desacoplamento estimada) gerando a corrente desejada  $(i_{ds}^*)$ . A diferença entre esta corrente  $(i_{ds}^*)$  e a estimada pelo sistema  $(i_{ds})$  comanda o segundo "PI" do laço na geração da tensão de estator desejada no eixo girante d  $(V_{ds}^*)$ .

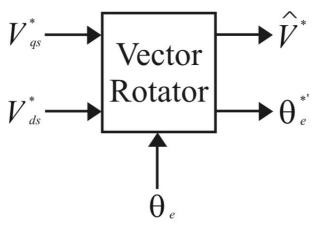

Como operação final realizada pelo bloco "Controlador", outro de seus subsistemas, chamado " $Vector\ Rotator$ " (figura 2.5), processa as saídas  $V_{qs}^*$  e  $V_{ds}^*$  geradas pelo subsistema "Laços de Controle de Torque e Fluxo".

Figura 2. 5 - Subsistema "Vector Rotator".

Este processamento realizado pelo subsistema "Vector Rotator" é descrito pelas equações 2.17 e 2.18, consistindo no cálculo de representação do vetor magnitude de tensão  $(\hat{V}^*)$  e no cálculo do ângulo de orientação deste vetor  $(\theta_e^{*'})$ .

$$\hat{V}^* = \sqrt{(V_{qs}^*)^2 + (V_{ds}^*)^2}$$

(2.17)

$$\theta_e^{*'} = \theta_e + \tan^{-1} \left( \frac{V_{qs}^*}{V_{ds}^*} \right)$$

(2.18)

No protótipo composto por DSP mais FPGA deste trabalho, o bloco "Controlador", como o bloco "Estimador de Sinais" já descrito, está construído como uma rotina de programação para execução pelo DSP. Um usuário externo interage com o bloco "Controlador" através de uma interface com usuário interligada ao DSP. Maiores detalhes sobre os circuitos constituintes desta interface e sobre o funcionamento do bloco "Controlador" construído, são fornecido no capítulo 4.

As saídas do subsistema " $Vector\ Rotator$ " ( $\hat{V}^*$  e  $\theta_e^{*}$ ) são aplicadas às entradas do bloco "Controle PWM Space-Vector Baseado em Redes Neurais", última unidade da seqüência de blocos constituindo o "Subsistema de processamento de sinais". Na seção a seguir são apresentados maiores detalhes a respeito do bloco "Controle PWM Space-Vector Baseado em Redes Neurais".

#### 2.4.4 Bloco Controle PWM Space-Vector Baseado em Redes Neurais

Este bloco recebe os sinais calculados pelo bloco "Controlador", ou seja,  $\hat{V}^*$  e  $\theta_e^{*'}$ , e os traduz em comandos de ativação (turn-on) e desativação (turn-off) (pulsos PWM) enviados para as chaves eletrônicas presentes no "Inversor baseado em IGBT"

(Subsistema de circuito de potência). O trabalho deste bloco consiste em propiciar uma modulação, a "*Space-Vector Modulation* ou SVM". A SVM, descrita em [10], representa um algoritmo com a finalidade de criar uma forma de onda desejada a partir de uma fonte de tensão constante "V<sub>d</sub>" (ou Link CC). Neste caso esta forma de onda desejada consiste em três senóides defasadas de 120 graus, com amplitudes e freqüências controladas, aplicadas aos terminais de entrada de um motor de indução. Para realizar seu trabalho o bloco "Controle PWM Space-Vector Baseado em Redes Neurais" conta com a estrutura representada na figura 2.6.

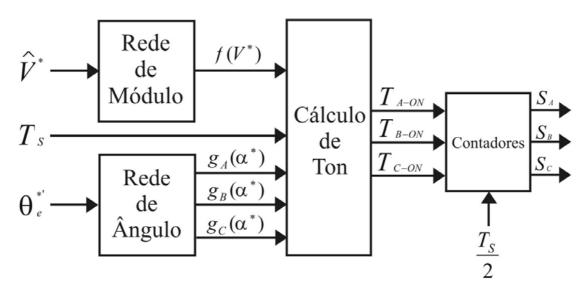

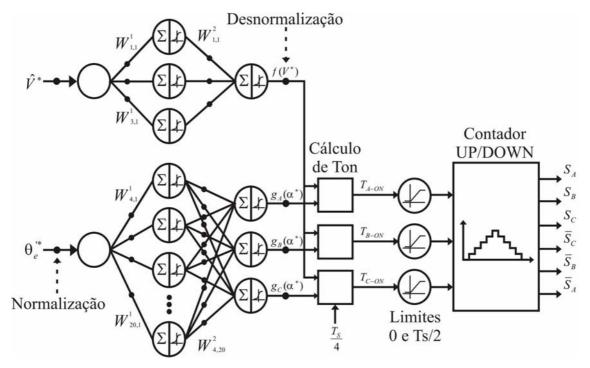

Figura 2. 6 - Diagrama do Controle PWM Space-Vector Baseado em Redes Neurais.

O diagrama da figura 2.6 mostra um subsistema que inicia processando as entradas  $\hat{V}^*$  e  $\theta_e^{*'}$  através de duas redes neurais: a de "Modulo" e a de "Ângulo", respectivamente. Maiores detalhes sobre a estrutura interna destas redes são fornecidos no capítulo 3. A "Rede de Módulo" realiza o cálculo da função  $f(V^*)$ , enquanto a "Rede de Ângulo" realiza os cálculos da função  $g_A(\alpha^*)$  para a fase A,  $g_B(\alpha^*)$  para a fase B e  $g_C(\alpha^*)$  para a fase C. As saídas  $f(V^*)$  e  $g(\alpha^*)$ , dentro do sub-bloco "Cálculo de Ton", são relacionadas com o período de amostragem dos sinais PWM  $(T_s)$  conforme as equações 2.19 a 2.21.

$$T_{A-ON} = f(V^*) \cdot g_A(\alpha^*) + T_s/4$$

(2.19)

$$T_{B-ON} = f(V^*) \cdot g_B(\alpha^*) + T_s/4$$

(2.20)

$$T_{C-ON} = f(V^*) \cdot g_C(\alpha^*) + T_s/4$$

(2.21)

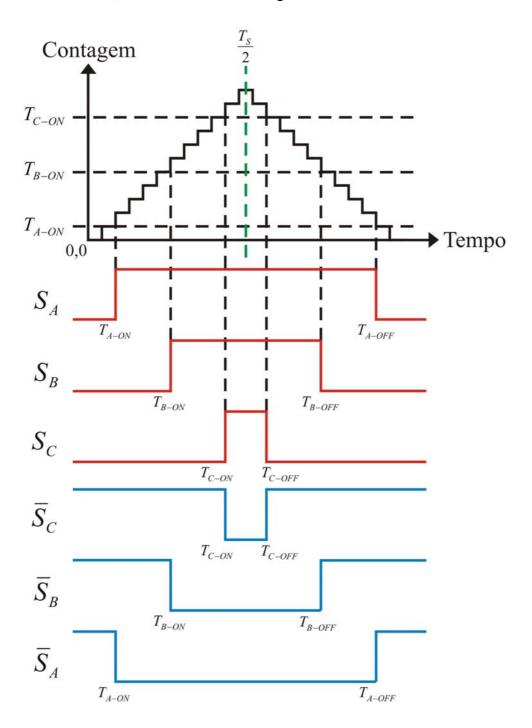

Os três tempos de "turn-on" ( $T_{A-ON}$ ,  $T_{B-ON}$ ,  $T_{C-ON}$ ) são utilizados como entradas para o sub-bloco "Contadores" na figura 2.6. Neste sub-bloco está um contador do tipo crescente/decrescente, responsável por gerar uma forma de onda triangular de período " $T_S$ ". Comparando-se esta onda triangular com os tempos de "turn-on" obtêm-se os sinais PWM de saída, conforme ilustrado na figura 2.7.

Figura 2. 7 - Exemplo de geração de sinais PWM.

A figura 2.7 apresenta um exemplo de geração de onda triangular de referência simétrica e com instante de pico localizado em "Ts/2". Os tempos " $T_{A-ON}$ ", " $T_{B-ON}$ ", " $T_{C-ON}$ " são representados na figura por linhas tracejadas horizontais. As saídas PWM " $S_A$ ", " $S_B$ ", " $S_C$ " estão representadas como ondas em vermelho, enquanto suas opostas (" $\overline{S}_A$ ", " $\overline{S}_B$ ", " $\overline{S}_C$ ") são representas por ondas em cor azul. Conforme pode ser notado da figura 2.7, a geração de um pulso em uma saída ocorre somente quando o valor de contagem (na triangular) for maior que a linha horizontal representando o tempo de "turn-on" relacionado com a saída. Variações no comprimento dos pulsos são obtidas deslocando-se para cima ou para baixo as linhas tracejadas horizontais, representando dos tempos de ativação.

#### 2.5 Considerações finais

O controlador do motor de indução descrito de forma geral, neste capítulo, é composto por vários blocos formando um sistema em malha fechada, executando um trabalho computacionalmente intensivo e exigente de alta velocidade de processamento. Esta modelagem do sistema, desenvolvida em trabalhos anteriores, visa unificar em uma abordagem uma estratégia de modulação vetorial e uma estratégia de estimação das grandezas do motor, ambas baseadas em redes neurais artificiais. Antes de ser apresentada a contribuição deste trabalho, ou seja, a arquitetura de hardware do protótipo desenvolvido, o capítulo 3 detalha as estruturas internas das redes neurais de modulação e estimação mencionadas. Estas estruturas representam bagagem de conhecimento, desenvolvida em trabalhos anteriores, que serviu como base para o início deste trabalho.

### CAPÍTULO 3 - ESTRUTURA INTERNA DOS BLOCOS "CONTROLE PWM SPACE-VECTOR BASEADO EM REDES NEURAIS" E "ESTIMADOR DE FLUXO"

#### 3.1 Introdução

O capítulo 2 apresentou de forma geral todos os blocos envolvidos no funcionamento do controlador do motor de indução deste trabalho. Neste capítulo, serão descritas as estruturas internas dos blocos "Controle PWM Space-Vector Baseado em Redes Neurais" e "Estimador de Fluxo". No capítulo 4, são apresentadas arquiteturas de hardware para implementação de todos os blocos do "Subsistema de Processamento de Sinais". A seção a seguir inicia o capítulo, apresentando a modelagem neural do bloco "Controle PWM Space-Vector Baseado em Redes Neurais".

#### 3.2 Estrutura do bloco "Controle PWM Space-Vector Baseado em Redes Neurais"

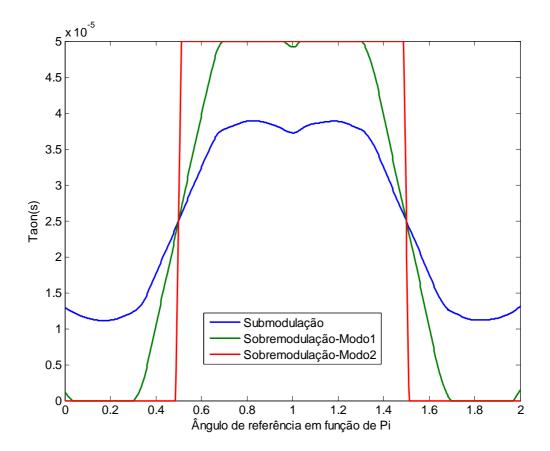

Conforme já mencionado no capítulo 2, o bloco "Controle PWM Space-Vector Baseado em Redes Neurais" traduz valores de magnitude e ângulo de referência em comandos de entrada em condução (turn-on) e bloqueio (turn-off). Estes comandos são enviados como pulsos PWM para chaves eletrônicas presentes no módulo "Inversor baseado em IGBT" ("Subsistema de circuito de potência"). A modelagem do bloco "Controle PWM Space-Vector Baseado em Redes Neurais" foi inicialmente desenvolvida em [25] e [26]. Nestes trabalhos foram obtidas expressões para os tempos de condução e bloqueio através de testes do algoritmo SVM. Estas expressões, depois de simplificadas e unificadas permitiram expressar os tempos de condução e bloqueio de forma gráfica como funções do ângulo de referência de modulação " $\theta_e$ ". A figura 3.1 apresenta exemplos destes gráficos de tempo de ativação para três regiões de modulação diferentes. As curvas da figura 3.1 foram geradas utilizando um período de amostragem "Ts" igual a 100µs (um dos valores preestabelecidos em [25] e [26]). Três regiões de modulação foram consideradas: Submodulação, Sobremodulação-Modo 1 e Sobremodulação-Modo2.

Figura 3. 1 - Gráficos de tempo de ativação gerados por SVM.

O que diferencia uma região de modulação da outra é o chamado índice de modulação (m). O índice de modulação varia entre 0 e 1, sendo expresso pela equação 3.1.

$$m = \frac{V^* \cdot \pi}{2 \cdot Vd} \qquad (3.1)$$

Na equação 3.1 o índice de modulação "m" está relacionado com a magnitude da tensão de referência "V\*" e com a tensão de "Link CC" (ou "V<sub>d</sub>", como já apresentado na descrição do "Subsistema de Circuito de Potência" no capítulo 2). A região de Submodulação é definida pelo intervalo 0<m<0,907, a região de Sobremodulação-Modo 1 é definida pelo intervalo 0,907<m<0,952, e a região de Sobremodulação-Modo 2 pelo intervalo 0,952<m<1. Graficamente, as diferenças entre as regiões de modulação ficam evidentes, conforme pode ser notado na figura 3.1. A curva de tempo de ativação para região de Submodulação (azul) não apresenta "achatamentos" como ocorre para os valores de "Ta-on" iguais a 0 e "Ts/2" na curva para a região de "Sobremodulação-

Modo1" (verde). Já a curva para região de "Sobremodulação-Modo 2" (vermelha) apresenta-se praticamente quadrada, e também está limitada entre 0 e "Ts/2".

Utilizando os dados de tempo de ativação mencionados, as redes neurais utilizadas neste trabalho foram modeladas e treinadas em [25] e [26] para depois comporem o bloco "Controle PWM Space-Vector Baseado em Redes Neurais". Um diagrama destas redes é apresentado na figura 3.2.

Figura 3. 2 - Diagrama do Controle PWM Space-Vector Baseado em Redes Neurais.

A figura 3.2 apresenta tanto a "Rede de módulo" (rede no topo da figura) quanto à "Rede de ângulo", como redes MLP (Multi Layer Perceptron), treinadas utilizando o algoritmo "Back-Propagation". A "Rede de módulo" é composta por uma camada de entrada com três neurônios e uma camada de saída composta por um neurônio. Todos os neurônios possuem função de ativação sigmóide e trabalham com pesos sinápticos fixos. Já a "Rede de ângulo" apresenta estrutura mais complexa, contando com 18 neurônios na camada de entrada e três neurônios na camada de saída. Também nesta rede todos os neurônios ponderam suas entradas com pesos fixos e geram saídas a partir de funções de ativação sigmoidais. Operações de normalização de entradas e desnormalização de saídas finais, realizadas pelas duas redes neurais, traduzem valores manipulados dentro das redes para escalas correspondentes ao restante do sistema.

As saídas pós-normalizadas da "Rede de módulo" ( $f(V^*)$ ) e da "Rede de ângulo"  $(g_A(\alpha^*), g_B(\alpha^*))$  e  $g_C(\alpha^*)$  são utilizadas juntamente com a entrada "Ts/4" em três módulos multiplicadores e acumuladores, obtendo-se como resultados os valores de tempo de ativação: " $T_{A-ON}$ ", " $T_{B-ON}$ ", " $T_{C-ON}$ ". Estes tempos após passarem por blocos que os limitam entre 0 e "Ts/2", são aplicados aos "Contadores UP/DOWN" para geração dos sinais PWM, conforme já explicado no capítulo 2. Os blocos de limitação entre 0 e "Ts/2" causam os "achatamentos" observados nas curvas de tempo de ativação das regiões de Sobremodulação dos modos 1 e 2.

No módulo "Inversor baseado em IGBT" ("Subsistema de circuito de potência"), as saídas de PWM " $S_A$ ", " $S_B$ ", " $S_C$ ", " $\overline{S}_A$ ", " $\overline{S}_B$ ", " $\overline{S}_C$ " acionam IGBTs pertencentes aos três "ramos" diferentes, conforme mostrado na figura 3.3.

Figura 3. 3 - Interconexão das saídas PWM com inversor de potência e MIT.

Na figura 3.3 a saída " $S_A$ " e sua oposta " $\overline{S}_A$ " formam o ramo correspondente à fase A do sistema, o par " $S_B$ " e " $\overline{S}_B$ " corresponde à fase B, enquanto " $S_C$ " e " $\overline{S}_C$ " representam a fase C, aplicadas ao motor de indução (MIT).

Maiores detalhes sobre técnicas e ferramentas de programação para modelagem e treinamento da "Rede de módulo" e da "Rede de ângulo" estão em [25] e [26]. A seção a seguir abre a segunda parte deste capítulo, descrevendo a estrutura do bloco "Estimador de Fluxo".

#### Estrutura do bloco "Estimador de Fluxo" 3.3

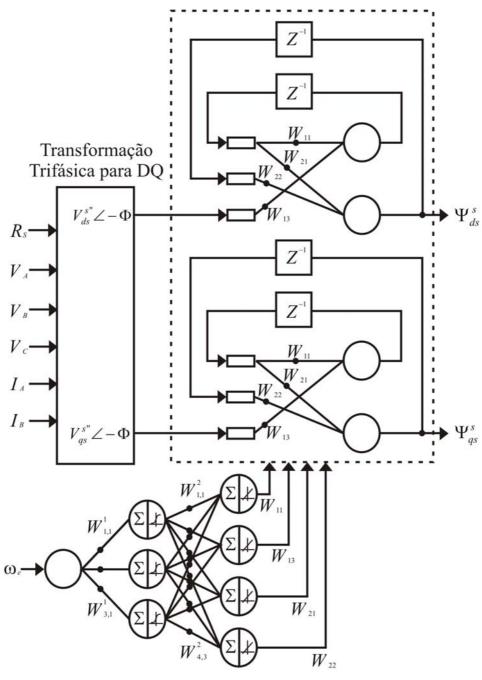

Informações sobre a planta controlada, no caso o motor de indução, devem ser obtidas para permitir que um controlador em malha fechada possa alterar adequadamente parâmetros controlados desta planta. A estimação é um método indireto de aquisição de informação sobre a planta, substituindo o uso de sensores considerados inviáveis. O bloco "Estimador de Fluxo" estima o fluxo estatórico do motor de indução através da estrutura de rede apresentada na figura 3.4, idealizada anteriormente em [25].

Figura 3. 4 - Redes recorrente e MLP compondo a "RNN-MLP".

A figura 3.4 apresenta um sistema híbrido (rede RNN-MLP), composto por duas redes neurais interligadas. O propósito deste sistema é a estimação de fluxo de estator através de uma estratégia de integração utilizando estágios cascateados de filtros passa baixa (PCLPF), modelados utilizando redes neurais. Segundo [25], esta estrutura de PCLPFs permite a realização de integrações de tensões de entrada dentro de uma larga faixa de frequência, sem o efeito indesejável de deslocamento (offset) CC na resposta.

A rede neural na parte inferior da figura 3.4, uma MLP, é composta por uma camada de entrada com três neurônios com função de ativação sigmóide, e uma camada de saída com quatro neurônios com função de ativação linear. Esta rede recebe uma única entrada, "\omega\_e" (frequência de rotação), gerada e normalizada pelo bloco "Estimador de Sinais", apresentado no capítulo 2, seção 2.2. A cada novo início de ciclo de trabalho, a rede MLP usa " $\omega_e$ " para gerar, como saída, quatro sinais representados pesos: " $W_{11}$ ", " $W_{13}$ ", " $W_{21}$ ", " $W_{22}$ ". Para efetuar seus cálculos, esta rede MLP conta com uma matriz de pesos sinápticos fixos, obtidos por treinamento realizado em trabalho anterior [25].

A rede localizada na parte superior da figura 3.4 (no interior do retângulo tracejado) corresponde a uma RNN (rede neural recorrente). Esta rede possui como entradas pesos sinápticos variáveis, ou seja, as saídas " $W_{11}$ ", " $W_{13}$ ", " $W_{21}$ ", " $W_{22}$ " da rede MLP. Como entradas, esta rede recebe as tensões " $V_{as}^{s"} \angle -\Phi$ " e " $V_{ds}^{s"} \angle -\Phi$ ", resultantes dos cálculos do bloco "Transformação Trifásica para DQ" (à esquerda na figura 3.4).

O bloco "Transformação Trifásica para DO" realiza uma transformação de espaço de representação das entradas da rede "RNN-MLP". Esta transformação (transformada de Park) obtém as tensões " $V_{qs}^{s"} \angle -\Phi$ " e " $V_{ds}^{s"} \angle -\Phi$ ", a partir de entradas medidas diretamente dos terminais de entrada do motor de indução do sistema. Estas entradas são as correntes de fase " $I_A$ ", " $I_B$ ", e as tensões de fase " $V_A$ ", " $V_B$ ", " $V_C$ ". Além destas entradas, é utilizado um parâmetro construtivo do motor, ou seja, a resistência de estator ( $R_s$  na figura 3.4), obtida por meio de ensaios práticos. Devido à necessidade prática de pré-filtragem dos sinais de tensões e correntes utilizados como entradas pelo bloco "Transformação Trifásica para DQ", as tensões de saída " $V_{as}$ " e " $V_{ds}$ " estão representadas na figura 3.4 com um deslocamento de fase "- $\Phi$ ".

A rede RNN-MLP é sistema com memória, ou seja, utilizam em seus cálculos atuais valores obtidos, anteriormente, pela própria rede. Esta característica de trabalhar com dados atrasados no tempo é representada pelos blocos "Z<sup>-1</sup>" na figura 3.4. Além disso, as funções de ativação dos neurônios da rede "RNN" não são representadas na figura 3.4, já que estes neurônios correspondem a blocos multiplicadores de duas entradas.

Como saídas, a rede RNN gera os fluxos " $\Psi_{ds}$ " e " $\Psi_{as}$ ", representando projeções nos eixos "d" e "q" do fluxo de estator no instante de amostragem, pelo bloco "Estimador de Fluxo", das entradas " $I_A$ ", " $I_B$ ", " $V_A$ ", " $V_B$ ", " $V_C$ ".

Detalhes sobre as técnicas de treinamento e ferramentas de modelagem, utilizadas na criação das redes do bloco "Estimador de Fluxo" são fornecidos em [25]. Resultados de operação destas redes são apresentados no capítulo 5 deste trabalho.

#### **3.4** Considerações finais

O capítulo 4 voltará a descrever todos os blocos do "Subsistema de processamento de sinais" analisados neste capítulo e no capítulo 2. Porém, haverá enfoque para a descrição da arquitetura e do funcionamento do hardware utilizado na implementação de cada um desses blocos. Tal enfoque faz uso da teoria de máquinas de estados finitos, de conceitos relacionados com linguagens de descrição de hardware (VHDL), e de conceitos sobre representação numérica em ponto flutuante.

Detalhes adicionais sobre algoritmo SVM e estimação de sinais em controle "sensorless" podem ser encontradas em [25] e [26].

# CAPÍTULO 4 - DESCRIÇÃO DO HARDWARE DO SISTEMA PROPOSTO

# 4.1 Introdução

Neste capítulo, o "Subsistema de Processamento de Sinais" é novamente analisado, porém, o enfoque está na descrição da arquitetura e do funcionamento do hardware desenvolvido para implementá-lo. Este hardware representa a parte experimental, isto é, o protótipo propriamente dito do trabalho. Os resultados experimentais sobre seu funcionamento serão apresentados no capítulo 5.

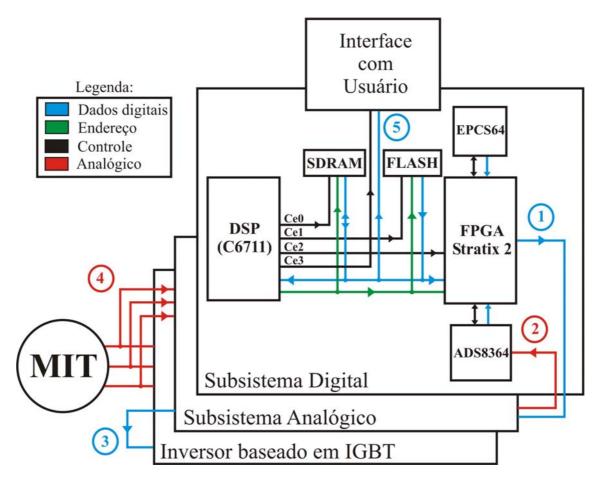

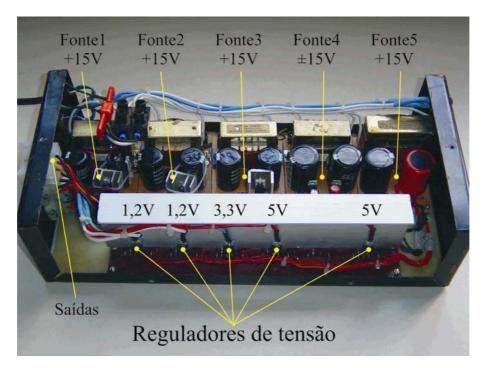

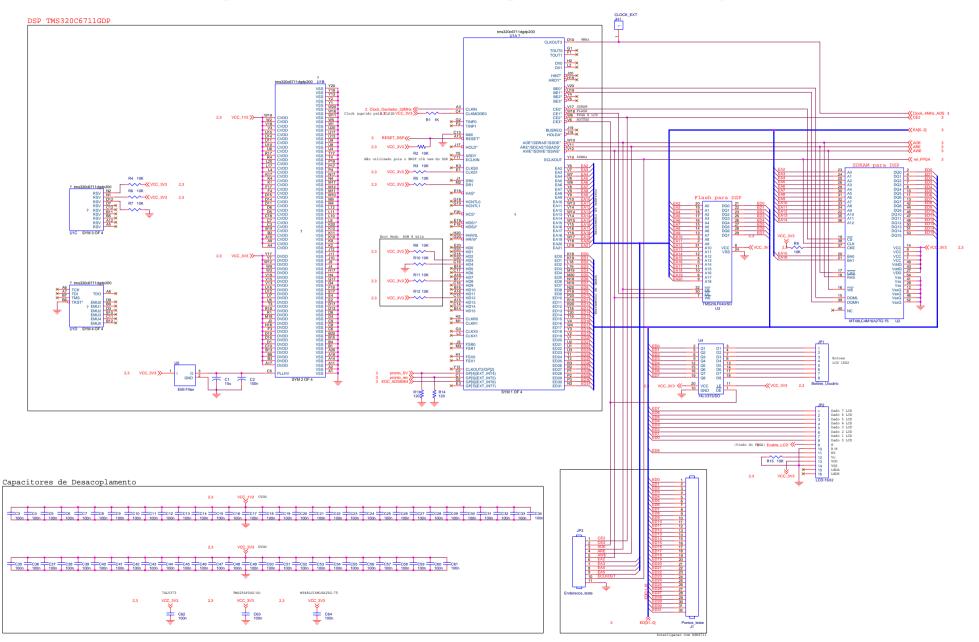

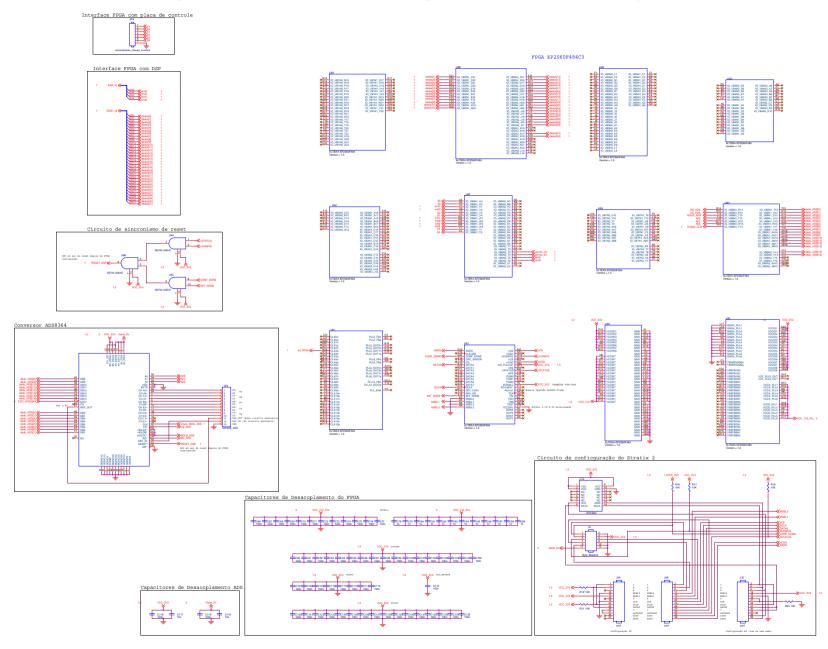

# 4.2 Descrição geral

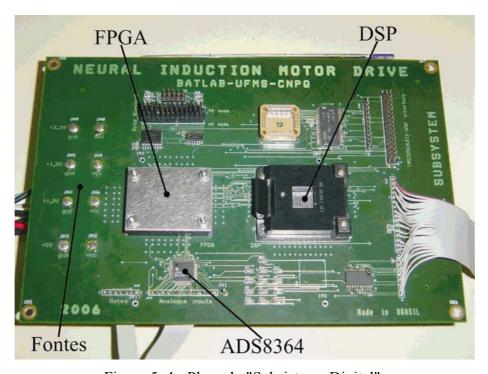

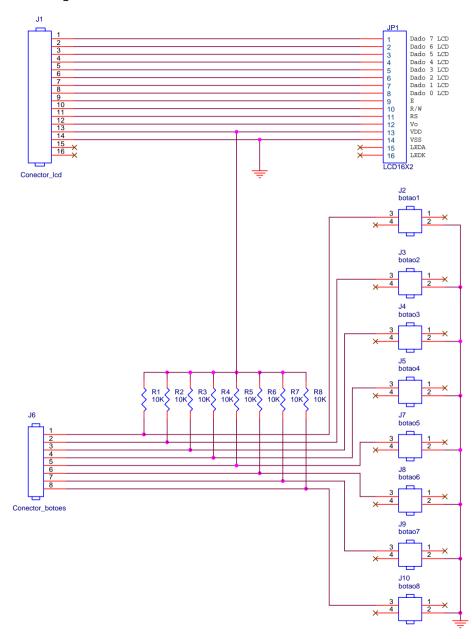

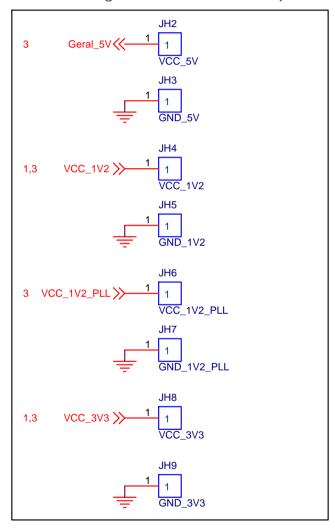

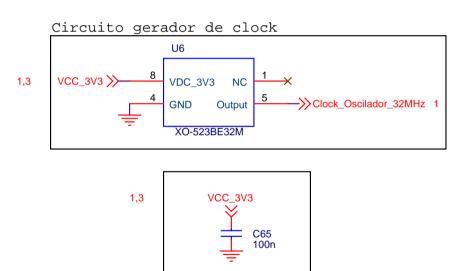

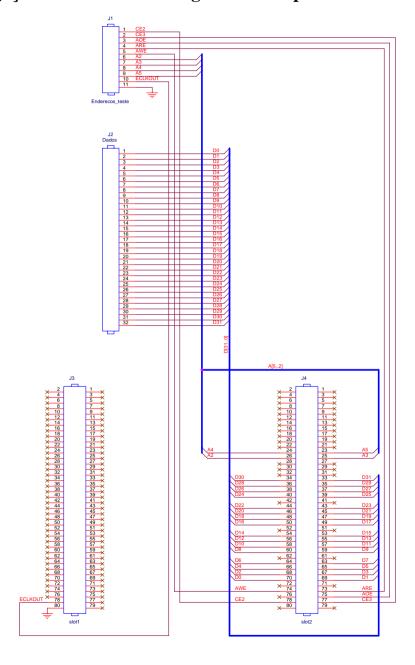

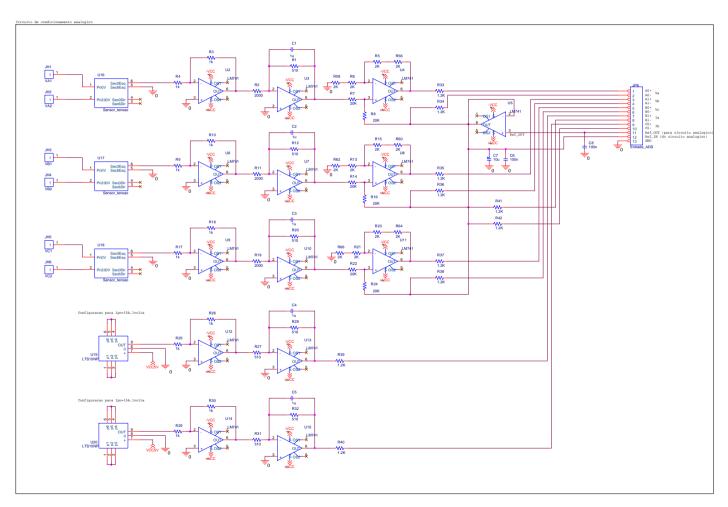

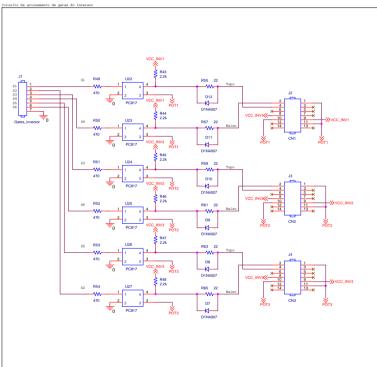

O hardware do "Subsistema de processamento de sinais" é um protótipo fisicamente composto por três placas de circuito impresso (PCIs): o "Subsistema Digital", o "Subsistema Analógico", e a "Interface com o Usuário". O "Subsistema Digital" representa o circuito de processamento digital central, contendo o DSP (um TMS320C6711 da *Texas Instruments*), o FPGA (um Stratix 2 EP2S60F484C3 da *Altera*), um conversor analógico para digital (ADS8364), além de outros circuitos de suporte (como memórias, registrador paralelo, portas lógicas, gerador de sinal de clock, etc.).

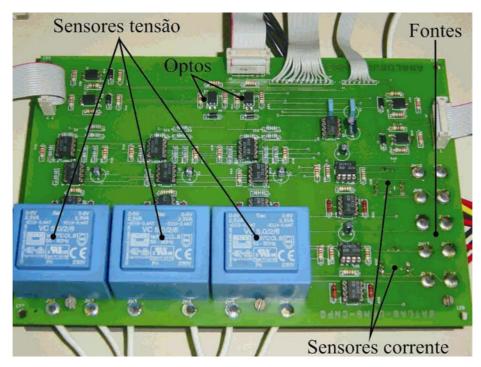

O "Subsistema Analógico" corresponde a um conjunto de circuitos analógicos divididos para atender duas tarefas distintas: leitura e condicionamento de sinais de tensões e correntes obtidos do MIT, e circuito de comando de *gate* das chaves de potência do "Inversor baseado em IGBT". A função de leitura é realizada utilizando sensores de tensão AC (transformadores de medição) e sensores de corrente por efeito Hall. A função de condicionamento de sinais é realizada por filtros "passa-baixa" construídos utilizando amplificadores operacionais. Já a função de gatilho das chaves de potência do Inversor é realizada por circuitos opto-acopladores para isolação e conversão de níveis de tensão de gatilho (do nível digital 3,3V para o nível de potência 15V).

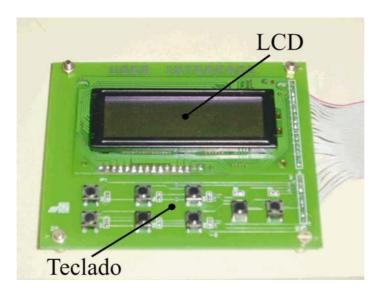

A "Interface com o Usuário" representa um circuito impresso com display de cristal líquido (LCD) e teclado. A partir deste circuito o usuário visualiza o estado do sistema e entra com parâmetros de funcionamento desejados. O diagrama da figura 4.1 apresenta uma idéia geral da arquitetura do protótipo proposto neste trabalho.

Figura 4. 1 - Protótipo do controlador do MIT baseado em redes neurais.

Na figura 4.1 são evidenciadas as três placas de circuito impresso mencionadas: o "Subsistema Digital", o "Subsistema Analógico" e a "Interface com o Usuário". Além disso, estão representados os componentes de potência "Inversor baseado em IGBT" e MIT (máquina de indução trifásica).

Os números 1, 2, 3, e 4 circunscritos, presentes na figura 4.1, realçam algumas das interligações importantes. O número 1 representa o conjunto de seis saídas digitais PWM ( $S_A$ ,  $S_B$ ,  $S_C$  e suas opostas), vindas do FPGA, servindo como circuito de comando das chaves de potência do inversor por meio dos circuitos opto-acopladores no "Subsistema Analógico". O número circunscrito 3 representa as próprias ligações dos circuitos opto-acopladores no "Subsistema Analógico" com os circuitos de acionamentos dos IGBTs (chaves) no inversor de potência. O número 2 representa o conjunto de sinais de tensão e corrente da MIT, lidos pelos sensores no "Subsistema Analógico" e convertidos para digital pelo conversor (ADS8364) no "Subsistema Digital". O número 4 representa a interligação do "Inversor baseado em IGBT" com a MIT e, além disso, a interligação dos terminais de entrada da MIT com os sensores de

tensão e corrente no "Subsistema Analógico". O número 5 representa o barramento de controle e de dados interligando a "Interface com o Usuário" com a placa do "Subsistema Digital".

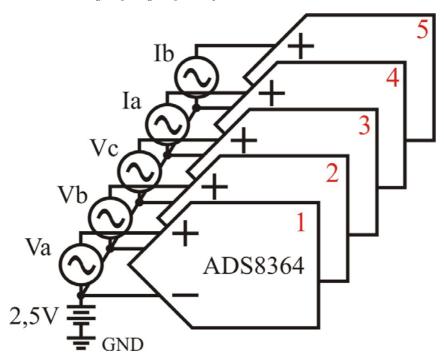

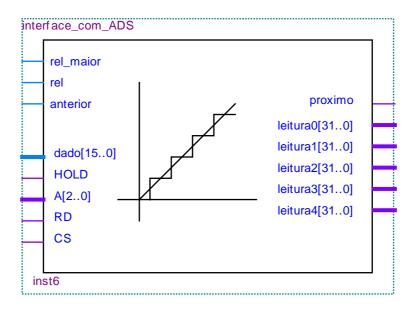

Conforme mostrado na figura 4.1, juntamente com o DSP e o FPGA, o "Subsistema Digital" ainda inclui os módulos importantes: "SDRAM", "FLASH", "EPCS64", e "ADS8364". A "SDRAM" constitui uma unidade de memória volátil para armazenamento de variáveis manipuladas pelo sistema operativo do DSP e de variáveis utilizadas nos cálculos matemáticos do DSP. O módulo de memória não volátil "FLASH" armazena o programa executado pelo DSP. Este programa é transferido para o DSP através de um processo de *boot* do próprio DSP. O módulo "EPCS64" também é uma memória não volátil, porém, sua função é armazenar um arquivo de configuração enviado para o FPGA durante o processo de *boot* do FPGA. Por fim, o módulo "ADS8364" representa, como já mencionado, o conversor analógico para digital. Este conversor digitaliza cinco sinais analógicos vindos do "Subsistema Analógico" a cada ordem de início enviada pelo FPGA. Os resultados destas conversões são utilizados pelo FPGA em seus cálculos internos. Os módulos mencionados brevemente nesta seção de descrição geral serão descritos com mais detalhes nas seguintes, conforme for sendo oportuno.

O enfoque deste capítulo está na descrição do hardware do protótipo do controlador do motor de indução utilizando como base a discussão dos capítulos 2 e 3. Seguindo esta idéia, os blocos do controlador do MIT serão descritos seguindo a ordem obedecida no capítulo 2, ou seja: "Estimador de Fluxo", "Estimador de Sinais", "Controlador", e "Controle PWM Space-Vector Baseado em Redes Neurais". Fisicamente, estes são sistemas implementados pelo núcleo de processamento DSP mais FPGA, pertencente ao "Subsistema Digital". Porém, como um ciclo completo de controle do MIT envolve também o "Subsistema Analógico" e a "Interface com o Usuário", serão inicialmente apresentados subsistemas não mencionados no capítulo 2.

Na seção a seguir será descrito o "Subsistema Analógico" do controlador do motor de indução. Seguindo um encadeamento de sistemas, nas seções posteriores serão descritos os blocos do "Subsistema Digital" em si. O objetivo é finalizar o capítulo com uma descrição da malha fechada, compondo o "Subsistema de Processamento de Sinais" como um todo.

# 4.3 Subsistema Analógico (medição e condicionamento de sinais)

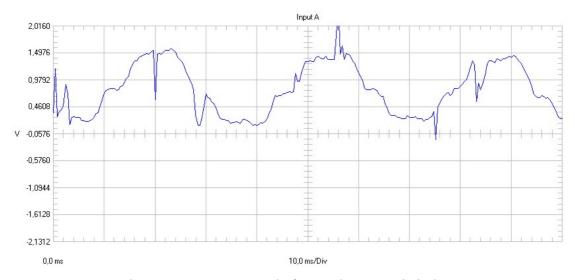

Cada ciclo de trabalho do controlador do motor de indução proposto inicia-se pela medição de tensões e correntes dos terminais de entrada do motor controlado. Esta tarefa é realizada pelos elementos na placa de circuito impresso do "Subsistema Analógico". Basicamente, os circuitos do "Subsistema Analógico" realizam medição e condicionamento de sinais coletados dos terminais de entrada da MIT. A figura 4.2 mostra um diagrama dos estágios envolvidos para a medição de tensões de entrada da MIT.

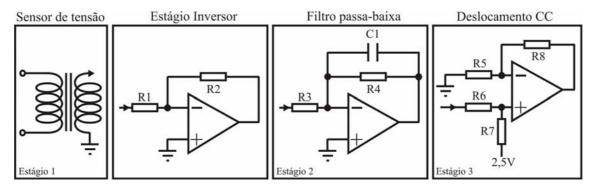

Figura 4. 2 - Medição de tensão de entrada da MIT.

A figura 4.2 representa um diagrama de circuito de medição de tensão de fase na entrada do MIT. O protótipo real replica o sistema da figura 4.2 três vezes, uma vez para cada tensão trifásica necessária ( $V_a$ ,  $V_b$ ,  $V_c$ ). No diagrama da figura 4.2, o estágio 1 representa um sensor de tensão, físicamente representado no protótipo por um transformador de medição que reduz a tensão de fase lida, de 220V AC para 6V AC. Já o estágio 2 apresenta uma dupla função, a primeira consiste em atenuar possíveis componentes de alta freqüência do sinal através de um filtro passa-baixa com freqüência de corte próxima a 300Hz. A segunda função consiste em atenuar a amplitude do sinal medido, tornando seu valor de pico a pico dentro da faixa de -2,5V a +2,5V. Inevitavelmente, a existência de um filtro como o do estágio 2 causa um deslocamento de fase de 180 graus no sinal medido. Para corrigir este problema, no protótipo final foi incluído um "Estágio Inversor" (circuito com amplificador operacional na entrada do filtro do estágio 2 na figura 4.2). No estágio 3 o sinal filtrado fornecido pelo estágio 2 é deslocamento da faixa de -2,5V a +2,5V para a faixa de 0 a 5V. Este deslocamento do sinal para uma faixa acima de 0 é uma exigência para as entradas analógicas do

conversor ADS8364. Detalhes adicionais dos circuitos de medição de tensão estão no apêndice A deste trabalho.

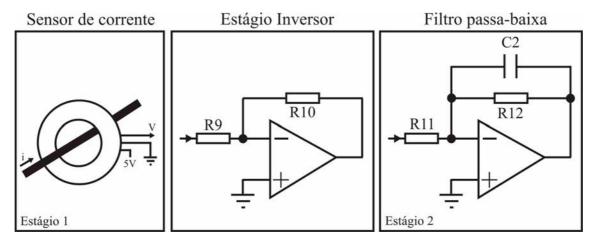

De forma análoga ao descrito para medições de tensão, medições de corrente também envolvem estágios, conforme mostrado na figura 4.3.

Figura 4. 3 - Medição de corrente.

Na figura 4.3 o estágio 1 representa um sensor Hall (LTS-15NP) alimentado por 5V e que transforma o valor de corrente de fase medido em um valor de tensão proporcional. Este valor de tensão já está dentro da faixa de 0 a 5V e é filtrado pelo circuito passa-baixa do estágio 2 após passagem pelo "Estágio Inversor" anterior. O circuito da figura 4.3 é replicado duas vezes na placa de circuito impresso do "Subsistema Analógico". Através desta replicação, é possível medir as correntes de fase  $I_a$  e  $I_b$ , sendo  $I_c$  obtida analiticamente conforme já mencionado no capítulo 2. Os circuitos completos para medição de corrente de fase podem ser encontrados no apêndice A deste trabalho.

O "Subsistema Analógico" realiza um processo de adequação das amplitudes dos sinais de corrente e tensão para compatibilidade com o padrão de entrada do conversor A/D. Porém, para possibilitar o processamento realizado pelos subsistemas que recebem estes sinais, é necessária a conversão destes sinais para representação digital. Tal tarefa é realizada pelo conversor descrito na seção a seguir, o ADS8364.

## 4.4 Conversão analógica para digital (ADS8364)